#### IConnect007 presents

Process Engineering: PCB Manufacturing's "Delta Force"

12

32

A Process Engineer's Guide to Effectively Troubleshooting PWB Defects

> Process Management: Doing It Right

...and Much More!

# April 2016

# THE PCB List works

"When I joined Cirexx last year I shared with my colleagues the positive experiences I've had with The PCB List.

We listed Cirexx with a detailed Showcase on The PCB List and it has resulted in quotes and orders!

The PCB List is not only brand and image must for all PCB manufacturers, but also another set of boots on the ground directly generating business."

- Al Wasserzug Sr. Business Development Manager at Cirexx International

# ...and it can work for you!

Over 3000 members are already registered and using THE PCB List.

Get Found! Upgrade to a Showcase and Start Quoting Today.

The best way to find a PCB fabricator, anywhere.

www.thepcblist.com

### ADVANCEMENTS IN THERMAL MANAGEMENT 2016

AUGUST 3-4, 2016 • DENVER, CO.

#### PRELIMINARY CONFERENCE PROGRAM RELEASED

The preliminary program has been announced for the 2016 Advancements in Thermal Management Conference. The program will feature speakers from industry leaders such as IBM Research and the IBM Advanced Thermal Lab, University of California - Riverside, Outlast Technologies/CoorTek, FUR, and many more.

#### Here are some of the presentations

- Chip-Embedded Pumped Two Phase Cooling IBM Research

- Thermal Properties of Freestanding Reduced Graphene

Oxide Films University of California Riverside

- CFD Simulation of Power Conversion: Sensitivity to Model Assumptions – IBM Advanced Thermal Lab

- Ceramic Microchannel Devices for Thermal Management Ceramatec, Inc.

- Ultrathin Thermal Ground Planes Kelvin Thermal Technologies

- Thermal Management for Device Hot Spots and Improved Battery Safety Outlast Technologies

- Advanced Materials and Process for High Performance Flip Chip STATS ChipPAC Inc.

- As Electronics Get Smaller, Infrared Plays a Greater Role in Thermal Management FUR

- Thermally Conductive Ceramics Performance and Applications Materion Ceramics

- Power Dissipation Limits for High-Performance Tablet Cooling Electronic Cooling Solutions

- Ceramic Design and Material Opportunities for Demanding Power Density Applications - CeramTec GmbH

Thermal 2016 will boast the largest program in the event's history with more sessions and several pre-conference workshops, making it the most comprehensive thermal educational conference experience in the industry. Sign up today.

Interested in Speaking? Contact Nick Depperschmidt at: Nickd@WebcomCommunications.com or 720-528-3770 x.III

Interested in Exhibiting? Contact Robert Schaudt at; RobertS@WebcomCommunications or 720-528-3770 x.II25

#### www.ThermalNews.com/Conferences

# April 2016 Featured Content

# **Process Engineering & Troubleshooting**

Process engineers (and PE types) are the worker bees of the industry. In addition to writing standards and specifications or presenting the technical papers at industry events, they stay busy behind the scenes—running tests, gathering data, coming up with new ideas, developing new products, and so forth. Our experts this month bring first-hand knowledge of the phenomenon known as process engineering.

- **12 Process Engineering: PCB Manufacturing's "Delta Force"** *by Joe Fjelstad*

- **16 A Process Engineer's Guide to Effectively Troubleshooting PWB Defects** *by Michael Carano*

- 32 Process Management: Doing It Right by Todd Kolmodin

- **38 Focusing on What Matters Most!** *by Renato Peres*

- **46** Flexible Circuits and Kaizen Events by Dave Becker

# Affordable Versatility

Introducing the nViant<sup>™</sup> HDI laser drilling platform.  $A CO_2$  laser solution from a proven leader in via drilling.

Lower your cost of ownership with an effective HDI solution for board and substrate laser processing.

#### learn more at esi.com

#### The Quiet Mainstreaming of HDI Manufacturing

by Chris Ryder, ESI | Feb. 2016, I-Connect007

Although design engineers have driven the evolution of the current class of mobile devices, primarily through addressing market demand for new form factor innovation, the push to meet the associated manufacturing challenges has been responsible for a revolution in PCB manufacturing. Click to continue reading...

Designed for Brilliance. Engineered for Production.

April 2016 Vol. 6, No. 4 thepcbmagazine.com

#### HIGHLIGHTS

- 30 MilAero007

- 44 Supply Line

- 56 EIN Market

- 84 Top Ten PCB007

#### DEPARTMENTS

- 86 Events Calendar

- 87 Advertisers Index & Masthead

# More Content

#### ARTICLE

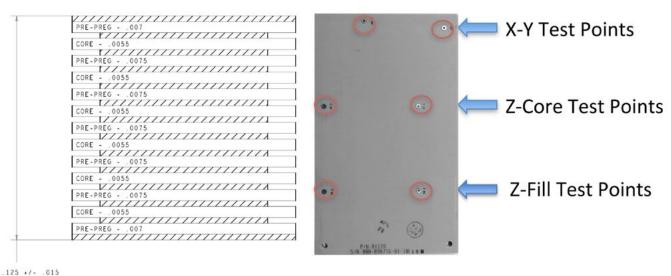

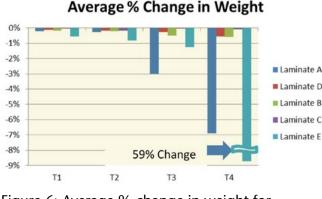

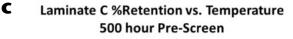

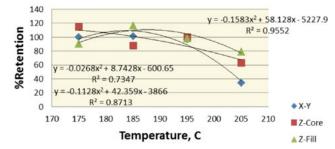

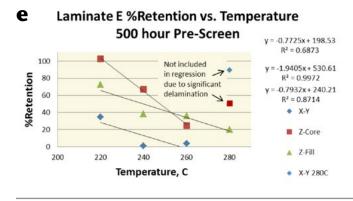

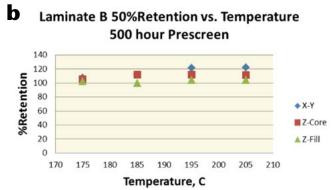

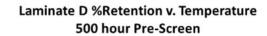

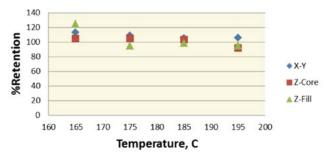

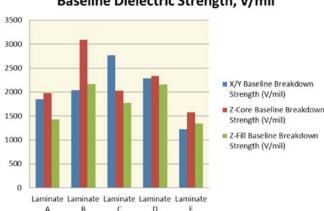

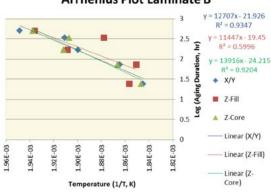

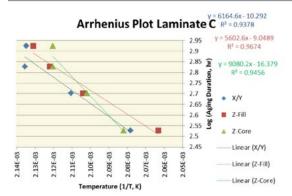

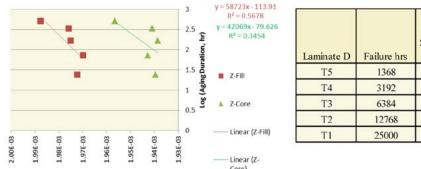

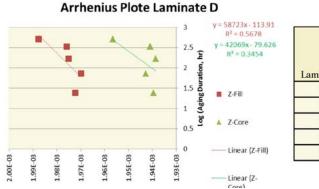

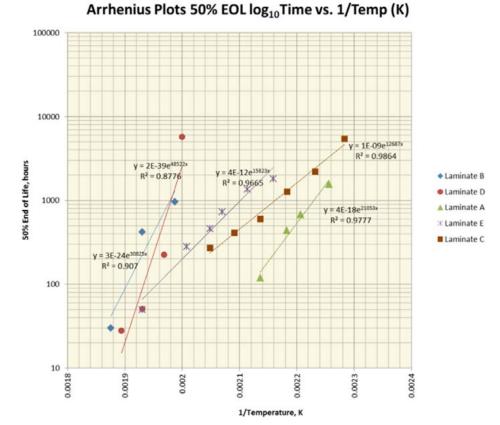

#### 58 Long-Term Thermal Reliability of PCB Materials

by Eva McDermott, Ph.D., Bob McGrath, and Christine Harrington

#### COLUMNS

8

- **A Salute to Process Engineers** by Patty Goldman

- 50 Best Practices: It's Only Common Sense by Steve Williams

#### SHORTS

- 28 Solberg and Holden: Two Valuable Series Available now at I-Connect007

- 36 Couldn't make it to the March Show(s)? Catch Up with Real*Time with*...Coverage!

- 54 I-Connect007 Exclusive: Walt Custer Elaborates on his IPC APEX EXPO Industry Forecast

# **185HR** High-Tg, Low-CTE Materials with High Thermal Reliability

#### **FEATURES**

- High Thermal Performance

- Tg: 180°C (DSC) (Base Laminate)

- ▶ Tď: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- · Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

- High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

Closest to conventional FR-4 processing

- Industry Approvals

- IPC-4101D-WAM1 /98 /99/ 101 /126

- UL File Number E41625

- Qualified to UL's MCIL Program

#### **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

- · Core Material Standard Availability

- Thickness: 0.002" (0.05 mm) to 0.060"/0.062" (1.5 mm)

- Àvailable in full size sheet or panel form

- Prepreg Standard Availability

- Roll or panel form

- Tooling of prepreg panels available

- · Copper Foil Type Availability

- Standard HTE Grade 3

- RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- Thinner copper foil available upon request

#### · Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

#### **ORDERING INFORMATION:**

Contact your local sales representative or visit www.isola-group.com for further information.

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd.Isola GmbHUnit 3512 - 3522, 35/FIsola StrassNo. 1 Hung To Road, Kwun Tong,<br/>Kowloon, Hong KongD-52348 Dür<br/>Phone: 49-2Phone: 852-2418-1318info-dur@isinfo.hkg@isola-group.comIsola Strass

Isola GmbH Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

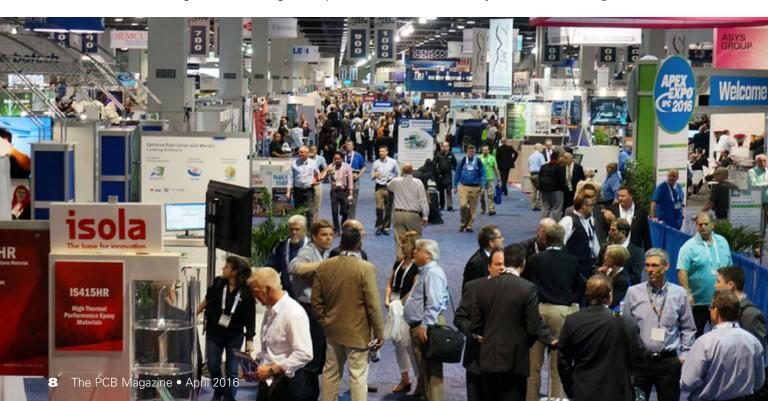

## **A Salute to Process Engineers**

#### by Patty Goldman I-CONNECT007

It seems very appropriate, coming on the heels of IPC APEX EXPO 2016, that the focus of our April issue is process engineering. I believe process engineers (and process engineer types) are the worker bees of IPC (and obviously of the companies they work for). If they don't actually write the standards and specifications or present the technical papers, they most certainly are doing the work behind the scenes—running tests, gathering data, coming up with new ideas, developing new products, making existing products work better, and so forth.

The interesting thing about process engineering in our industry is that you don't have to be a degreed engineer. You just have to be willing to take on the problem solving and troubleshooting that is involved in making things work—in this case, the PCB shop and its product. No easy task, believe me (I've been there) but the intrigue and the never-ending variety of problems, often brought on by the increasing complexity of PCBs, is probably what lured all of us in in the first place and keeps the job interesting and challenging—and makes it tough to leave. How many people do you know who have left the industry and found themselves drawn back in?

Getting back to the recent IPC conference and show, it was and is quite an event, as those in attendance can tell you. Between myriad subcommittee meetings, keynotes, a couple dozen technical paper sessions and the exhibition, one finds too much to do and way too little time to do it—and this year we had a lot of ground to cover. We certainly got plenty of walking in at the Las Vegas Convention Center; some people reached their 10,000 steps by noon!

In the meantime, though, there were more exhibitors than ever (though the PCB corner seemed smaller than ever) and there were many very interesting technical sessions where attendance was SRO. We hope to bring you some of those presentations in future issues of *The PCB Magazine*. The conference had special meaning to me, as I was inducted into IPC's Hall of Fame at the Tuesday luncheon, a huge honor and one

# Do you want the best via-to-pad alignment?

Use Tongtai's Single Station Drill Equipped with Nano System's Optical Registration System

Cognex™ Hi-Res Camera

- Machine vision seamlessly integrated with Sieb & Meyer<sup>™</sup> control

- Expose up to 21 layers with a single percussion countersink

- Enhanced illumination for skived layer targets

- Automatic and manual modes

Tongtai

- Vision data log files generated for each layer

- Target data can automatically integrate with Xact PCB<sup>™</sup> software

- Machine vision calibration & fiducial selection training included

- Optional precision depth control to  $\pm 20 \mu m$

- 160K rpm Westwind air bearing spindle

- Dependable North American service centers

#### contact us

Nano System, Inc. Milpitas, CA (408) 935-2270 Manchester, NH (603) 645-1500 sam.sekine@nanosystem-usa.com

**SD-116**

I am still trying to believe really happened. I am now an IPC Ambassador!

But let's talk more about this issue. I've started us off with Joe Fjelstad of Verdant Electronics who likens PCB process engineers to a "Delta Force." He gives us a great feel for what it is that a process engineer does and needs to do. His column should inspire and encourage all those in the figurative trenches, plus he points out some newly available resources.

This is followed by RBP Chemical's Mike Carano, back in action after a hiatus, with a fine article on troubleshooting. Mike is certainly an expert on this subject; he chairs the IPC Process Effects subcommittee and they have recently issued the latest rev of the troubleshooting guide, IPC-9121 "Troubleshooting for Printed Board Fabrication Processes," the first since 1997. Definitely a must have volume for every PCB manufacturer's bookcase.

Departing slightly from his usual testing subjects, Gardien's Todd Kolmodin gives us a wonderful, step-by-step guide to building and maintaining a robust process, stressing the importance of each step along the way.

Next, our newest columnist, Renato Peres of Circuibras in Brazil goes into some detail on DMAIC methodology used in Six Sigma. He includes the kind of practical, down-to-earth advice that process engineers want and need, having been there himself.

Another technique used in continuous improvement efforts is a Kaizen event, as Dave Becker of All Flex Flexible Circuits explains in his column. Perhaps not to be used lightly or for a quick fix, but a very useful tool for your process improvement toolbox.

As you can see, a good amount of process engineering involves process improvement and process streamlining, which is the essence of Lean and, as Steve Williams of the Right Approach shows us, not that complicated; in fact most of it is good old common sense.

We have a great technical article for you this month from Eva McDermott, et. al., of Amphenol Printed Circuit Board Technology, on the long-term thermal reliability of PCB materials. Just the sort of valuable, detailed study that engineers do (and yes, she is one).

Next month we will be focusing on strategies to reduce handling errors—and we're not just talking automation. See you then! **PCB**

**Patricia Goldman** is a 30+ year veteran of the PCB industry, with experience in a variety of areas, including R&D of imaging technologies, wet process engineering, and sales and

marketing of PWB chemistry. Active with IPC since 1981, Goldman has chaired numerous committees and served as TAEC chairman, and is also the co-author of numerous technical papers. To contact Goldman, <u>click here</u>.

### UcamX

New ground-breaking CAM Software

- For Rigid, Flex and HDI PCBs

- New Graphical User Interface with Workspaces

- Optimal performance using Parallel Processing

- Multi Job Processing via load balanced Sessions

- Support for Gerber version 2 (X2) format

<u>Ucamco</u>

PHOTOPLOTTERS

Read more  $\longrightarrow$

- Field proven with more than 450 installations in daily production

- Seamless integration into any CAM System

Field upgradable with new high resolution Nano AF100 Opto Electronics

SOFTWARE PHOTOPLOTTERS DIRECT IMAGERS NEWS SERVICES COMPANY DOWNLOADS CONTACT

For more information please contact info@ucamco.us, call (415) 508-5826 or check out our new website at www.ucamco.com

# **Process Engineering: PCB Manufacturing's "Delta Force"**

#### by Joe Fjelstad

The role of the process engineer is arguably one of the most important jobs in the printed circuit industry. The process engineer is on the front line of manufacturing and responsible for making sure product yields and profitability meet expectations. The job typically entails and intertwines many different and even disparate disciplines, including: electrochemistry, mechanical engineering, NC machining, robotics and automation, metallurgy, laser technology, polymer processing and photolithography. It even reaches back into the printed circuit design process. Because of this variety, it is also arguably at once, one of the most challenging and interesting jobs in the PCB industry.

In practice in most major manufacturing facilities, process engineers often specialize in just one of the areas identified here. In smaller facilities, the process engineer often must move between and attend to matters in more than one discipline, most commonly process steps which immediately precede or follow the area where the engineer has special training and expertise. However, in many cases, factors which may influence product quality and yield may be several steps earlier or later in the process. This is extremely important when one is looking into, or in the midst of implementing a new process on the manufacturing floor. Change comes slowly in PCB manufacturing and old habits are hard to break, so keeping a finger on the pulse of the process is critical.

It is a simple fact of life that in PCB manufacturing, process characterization, monitoring and maintenance are critical to success, and so also is collecting and evaluating data on process health. The tools and specific methods and measurements required will vary significantly from process to process, but without control, the quality of the results of the process will be left to a roll of the dice. One of the most important skills a process engineer should master

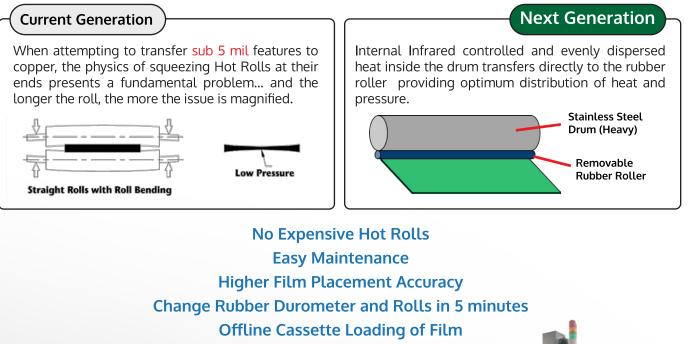

Hakuto, the 50 year leader in reliable dry film lamination for the PCB Industry introduces the first system that provides full and complete **EVEN** distribution of both **Heat and Pressure** across the entire surface of the PCB.

Easy removal of rollers with no tools (change of durometer rubber now possible)

### 630NP LAMINATOR

Ease of use and maintenance

Cassette loading offline reduces production film change to 5 minutes (multiple cassette cartridges available)

Supplier to the North American Circuit Board Industry since 1977 **Canada** 1124 Mid-way Blvd. Mississauga, ON L5T 2C1 P (905) 670-8400 **N. California** 3261 Edward Ave. Santa Clara, CA 95054 P (408) 477-2963 **S. California** 301 West Dyer Rd, Suite E Santa Ana, CA 92707 P (714) 825-0404

#### 800-668-5447 • www.matrixusa.us

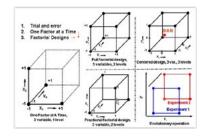

is learning how to properly design experiments to identify the optimal operating parameters for the target process. Selecting which variables to monitor and optimize is critical. One must first do the right things and then do things right. Pick the wrong ones and the data collected will likely be meaningless. And this begs the question: How does one choose variables to monitor in an experiment?

We are fortunately living in a time when there are oceans of experience in most of the processes used in circuit manufacturing, so tapping into that experience is important. There is no benefit in repeating experiments that have been run countless times before. In this regard, it is very important that the process engineer be at least as much a reader as an experimentalist. Running experiments is useful and can be engrossing but if the answers are known by others, it is better to tap into their knowledge base.

There is the old story of the successful individual who was queried as to the most important factor in their success. The two-word answer was "good experience." When pushed to explain how one gets the necessary good experience another two-word answer was given: "Bad experience." This apocryphal story was no doubt concocted by someone who understood the importance of learning from experiences and of the importance of failure. If we, in our infancy, were afraid of falling on our behinds as we departed infancy and attempted to walk, we would still be crawling about on our hands and knees. To this end there is the reminder from another sage, the early 20<sup>th</sup> century polymath and philosopher, G.K. Chesterton, who wrote: "Anything worth doing is worth doing badly." What is missing and must be inferred as an addendum to his message are the words, "...at first". There is nothing wrong with mistakes; mistakes are how we learn. However, if one has the resources available to them to avoid mistakes, then it is folly not to avail one's self of that information.

For the astute PCB process engineer, resources abound. There is a treasure trove of legacy information to be found in trade magazines, in academic journals, blogs, columns, supplier websites and industry specific texts. While on that thought, it is worth noting that *The Printed*  *Circuits Handbook,* now in its 50<sup>th</sup> year, has just been released in a 7<sup>th</sup> Edition, edited by PCB industry icons and gurus Clyde Coombs and Happy Holden. The tome has been both a bible and a source of intelligence for preparing battle plans for process engineers since its first edition and has been translated into several different languages. It arguably should be found on the reference bookshelf of any competent PCB vendor and more importantly it should be read...

There are, of course, numerous other repositories of process knowledge available. One easily overlooked are the individuals who represent the process or equipment developers. These individuals are the honey bees of the industry who help cross pollinate those within the industry with new ideas, transferring knowledge and experience between manufacturers to the betterment of all.

In summary, process engineers serve a vital function on the front line of printed circuit manufacturing. They are often, if you will, the "Delta Force" that subdues and controls that which is one of the mortal enemies of manufacturing...process variation. The intelligent process engineers should avail themselves of all of the tools they need to complete their mission. To that end and in reference and support of that last thought, it is highly recommended that the reader of this piece read the series of columns being prepared by Happy Holden for I-Connect007, titled "25 Essential Skills for Engineers." Holden's near half-century of experience and accumulated knowledge as PCB process engineer and manager are too important to let pass by unread. **PCB**

Verdant Electronics Founder and President **Joseph (Joe) Fjelstad** is a four-decade veteran of the electronics industry and an international authority and innovator in the field of electronic interconnec-

tion and packaging technologies. Fjelstad has more than 250 U.S. and international patents issued or pending and is the author of Flexible Circuit Technology. He is a frequent contributor to I-Connect007 publications. Flexibility = Simplicity = High quality = Reliability = Easy maintenance = Optimized investment

# The Latest Imager Technology © ED1500 Cost-Effective

**SWISS QUALITY** 720 x 610 mm 27.6" x 24"

The True Figures

Watch Demo Video

www.FirstElE.com US/Canada: cspitko@gmail.com

Europe: sbismuth@chimietech.com

### A Process Engineer's Guide to Effectively Troubleshooting PWB Defects

#### by Michael Carano

**RBP CHEMICAL TECHNOLOGY**

The printed wiring board fabrication process is an intricate maze of interrelated steps, both chemical and mechanical. A thorough understanding of each of the process steps is critical in minimizing or eliminating non-conforming defects—the ones that cost the fabricator money and can lead to lost customers. It is also critical to note that these profit-killing defects may have their origins elsewhere in the process.

That is the difficult thing about troubleshooting—the defect is often blamed on the process (such as electrodeposition of copper) because that is where the problem is first discovered. However, this is often false, as the origin of the defect may have had its humble beginnings in a previous process step.

To be successful at troubleshooting a problem, common sense usually applies. Basically one must first:

- Identify the problem or problems (be as specific as possible)

- Determine possible causes (looks for links to those other less obvious processes)

- Identify methods and procedures to test to see which causes apply

- Test the assumptions

- Implement corrective action

While this sounds like an oversimplification, this approach is required to properly identify and attack the problem at hand. A structured routine is really what is required.

In upcoming columns we will attempt to provide some insight as to the cause or causes of non-conforming defects and the potential solutions. We will discuss process parameters and the importance of control of the processes.

Let's discuss the step-by-step methodology for troubleshooting.

#### **Identify the Problem or Problems**

First and foremost, you must have a clear sense of what you are looking at. In troubleshooting, I firmly believe in the team approach to solving the problem. However, the team must agree on what the defect is: is it hole wall pull-away (HWPA) or resin recession; is this an interconnect defect (ICD) or simply a line of demarcation? These are just a few examples. But the wrong call will lead you down the incorrect

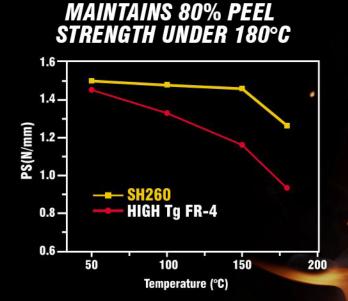

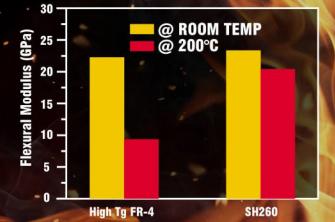

# Introducing SH-260, a new Polyimide system with Tg > 250°C (TMA) that provides ULTRA HIGH THERMAL PERFORMANCE

#### MAINTAINS 85% FLEXURAL STRENGTH UNDER 200°C

#### SH-260 IS IDEAL FOR:

- Burn-in boards

- Down Hole

- Aircraft and Aerospace

- Ultra-high count layer boards

- Other PCB high temperature/ long-duration applications

www.paramount-usa.com

path as you attempt to tech out of the problem.

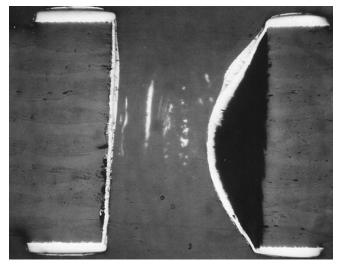

In Figure 1, examine the cross-section closely. Carefully determine if what one is seeing is a shrinking or recessing of the resin, or is the plated copper blistering or pulling away? Some would jump to the conclusion that the defect is HWPA. This would then trigger an exercise to brainstorm on a number of processes including desmear and electroless copper (including a deeper dive into drilling, electroless copper catalyzation and copper plating rates). However embarking on this path would be disastrous. Clearly the issue shown in not HWPA. The resin has recessed, leading to the proper conclusion that this is resin recession.

According to IPC-600 H, section 3.1.9, resin recession is acceptable for all classes of PCB boards after thermal stress.

Now, in the case of the defect shown in Figure 2, the plated copper clearly has lost adhesion to the hole wall.

When a condition such as HWPA is discovered, there are several potential causes of the defect:

**1.** Overactive electroless copper process: Essentially, the deposit is being laid down much

Figure 1: Defect clearly shows resin recession, not HWPA.

Figure 2: Severe case of HWPA.

too fast, leading to a stressed condition. The inherent stress in the deposit causes the copper to pull away from the substrate. Check the deposition rate on the electroless copper rate panelswas an increase noted possibly due to over temperature condition in the electroless copper solution? Is the chemistry out of balance? Check the formaldehyde, caustic and copper concentration. Is the process being controlled within the operating window of these additives? A higher than normal caustic concentration will lead to a higher deposition rate. Examine the grain structure of the electroless copper deposit. Compare to previous results when HWPA did not exist.

2. Desmear operation leaving a less than desirable surface topography on the resin: Typically, this is an issue related to the permanganate process. Higher Tg resins are more resistant to desmear chemistry and thus the surface topography and extent of resin removal are less than optimum. Weight loss measurements utilizing a small coupon made of the same resin system and processed through the desmear process under the current conditions will yield some evidence. An SEM taken of the PTH will give a good picture of the topography on the resin after desmearing. Do not rely on weight loss data alone. A sufficiently micro-roughened resin surface provides a surface area to promote catalyst adsorption as

# A new set of rules for PCB production

Less process steps. CAM to etch in minutes instead of hours. Maximum yield. Minimal environmental impact. These are just a few of the PCB production rules that Lunaris has redefined.

We've put together a complete set of all the new rules made possible by Lunaris ...get yours today!

Download all the new rules: The Official Lunaris Rulebook

CLICK HERE TO DOWNLOAD

www.mutracx.com

well as to provide anchoring sites for subsequent copper metalization. It is conceivable that the solvent swell (the first process step in the alkaline permanganate process) is not sufficiently weakening the polymer-polymer bonds in the resin. This will result in reduced resin removal and insufficient topography. First and foremost, the defect or issue must be properly identified in order to design a plan of attack. And again, I cannot stress enough the importance of up and downstream processing.

**66** First and foremost, the defect or issue must be properly identified in order to design a plan of attack.

Looking into methods to troubleshoot deeper, determine whether or not proper operating procedures were followed. Did the process change in some way from the standard? Compare the defective product to a non-defective one. Was the process operating within the specified parameters? Don't take anyone's word for it. Check this out thoroughly! On way too many occasions, significant loss has been incurred because the process or processes were run out of spec. *Famous last words: We checked everything an hour ago and all is good!*

Simple analysis or control procedures would have prevented such an occurrence. If the analysis shows that the chemistry, dwell times, operating temperatures, etc., are not in control, then bring the operation to a halt until the corrections are made. Then run some tests to see of these corrections solve the problem. If this does not correct the problem, then the team must sit down to determine other possible causes for the defect.

#### **Possible Causes**

The rule of thumb here is to keep the troubleshooting project as manageable as possible.

Begin to brainstorm on the linkages in the up and downstream processes and potential effects of process variation in these process steps. Gather all pertinent information including statistical process control (SPC) charts, temperature logs, analysis records (including record of calibration and analytical standards) and the like. Then develop a cause-and-effect diagram. Fish-bone diagrams serve this purpose well. At the risk of having hundreds of factors to investigate, only the most likely causes should be investigated first. This will serve to weed out those processes that are not contributing to the defect. A process audit is a must in this situation. Hopefully, you have a reliable supplier or suppliers who work with your company in close partnership. Ongoing process audits jointly and separately performed by your supplier and designated individuals in the fabricator's facility should be standard operating procedure. Process audits alert the manufacturer if a process is "drifting" out of the control window.

Once the team has set up its test plan based on a narrowing of potential causes, the divide and conquer approach will aid in the efforts. For example, if one suspects that thin plating of copper in the hole is caused by problems associated with the electrodeposition process, simply processing the PWB in the acid copper plating solution for the required time and current density should yield whether or not the copper plating process or the equipment (e.g., copper plating anodes, rectifier, electrical connections, etc.) are the cause. If not, then one must examine the previous steps. Are there discontinuities in electroless copper deposit or direct metalization process causing thin plating? Are there voids one cannot see? These are just some of the questions to be asked.

Only a systematic approach will help solve problems expeditiously. Above all, after selecting the processes and test procedures to be implemented, test these assumptions with vigor. Time is money.

Hopefully, these actions will identify the suspect cause(s) of the defect. When the problem is located, corrective action must be implemented. Determine what measures will be taken to ensure that the problem does not reoccur. Redefine the process control window. Set up

### We deliver world-class PCB CAM Engineering Services

Our global presence and 24/7 support helps enables our worldwide customers manage their workloads and grow their businesses.

"We needed a trusted partner to help us meet our front-end engineering requirements. Entelechy offered flexibility, expertise and a cost effective approach to our pressing needs. They have delivered on all of these fronts."

-Robert Jones President, Precision Technology, Inc.

VIEW COMPLETE SUCCESS STORY

"In our company, the CAM department was the bottleneck. As a result of our working with Entelechy, we can now accept orders that we had to refuse in the past."

HOFMANN Leiterplatten

-Thomas Hofmann CEO/Owner, Hofmann Leiterplatten

VIEW COMPLETE SUCCESS STORY

#### We can help your business, too.

Click here to learn about our No-Risk Quick-Start Program.

www.entelechyglobal.com

permanent controls in order to keep the process within a tighter operating window if necessary. For example:

- Set up process audits at specified times

- Implement process control procedures and measurements

- Preventative maintenance on equipment

- Training of operators

- Maintain or establish close ties with your suppliers

Certainly, this is only a guideline for troubleshooting. The key is to get to the root cause of the problem as soon as possible without taking shortcuts for the sake of time.

There is no substitute for a systematic approach backed by solid knowledge and understanding of the process parameters and the influences of up and downstream processes. Remember, the process in which the defect manifests itself is not always the main cause. Look carefully.

#### **Equipment Issues**

It is always quite easy when there is a significant issue to default to the chemical processes. What a mistake! A real life example is shown in Figure 3. The fabricator complained about incomplete etching of the copper, so it must be the fault of the chemistry. Upon examination by the tech team, there was a noticeable residue on the boards in some areas. This residue was inhibiting etching. However, the residue was deposited onto the circuit boards by the equipment rollers.

Note that the rollers were actually decomposing. However, this issue was not the fault of the etching solution. The issue relates to a purchase of roller materials that were not compatible with the chemistry. When in doubt read the equipment maintenance guide.

Here is another example of the failure to look at all aspects of the process (and that includes people, materials and machines).

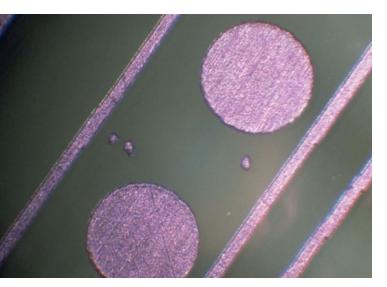

In Figure 4, the fabricator noted copper spots remaining on the innerlayers after develop-etch and strip. So the conventional wisdom is to look at the etching equipment and process chemistry. However, upon further review, it was

Figure 3: Transport wheels decomposing. (Source: IPC)

determined that only one part number showed copper spots. Other designs did not. As the photo in Figure 4 shows, there was exposed dry film resist that was protecting the underlying copper—as it should. However there was to be no exposed resist in this area. Upon examination of the particle phototool used for this part number, there were some very fine clear areas in what is the opaque portion of the tool. Thus, these pinholes allowed UV light to polymerize the resist in these areas. This in turn inhibited the etching, leaving copper spots. Clearly this was not a wet chemistry issue.

The above illustrates the importance of critical thinking (and knowledge) when troubleshooting PCB defects.

#### And if Things Couldn't be any Worse!

One of the most devastating issues to confront occurs when, despite the best efforts of the fabricator, the EMS company gives you a

#### **MIVA: LED Direct Imaging System**

- Industry leading Quad-wave Light Engine

- 4 wavelengths operating at high LED power

- 50 panels per hour from a single light engine

- Install up to 6 light engines

- Photoresist, solder mask, legend, silver film

- 50, 25, 10, 5, 2 micron feature resolutions

- Full automation systems available

- 3 year light source warranty

- Lowest system operating cost

#### Antares: X-Ray Optimization

- Precision X-Ray optimization

- Optional automatic load and/or unload

- Staggered or stacked targtets

#### Galaxy: XRO and Flash Removal

Mach3labs and VF Industries have coupled industry leading X-Ray Optimzation and automatic flash removal.

- X-Ray Optimize

- Flash Remove

- Edge Condition

- Corner Round

- Thickness Measure

- Panel Serialization

Kuper Technologies, LLC, PO Box 893, Concordville, PA 19331, Ph: (610) 620-3795 Eastern US: Brendan F. Hogan, M: (610) 620-3795, B.Hogan@KuperTek.com Western US: Kurt Weber, M: (714) 767-6367, Kurt@KuperTek.com MIVA: LED DIRECT IMAGING

Figure 4: Exposed resist due to pinholes in the phototool. (Source: IPC photo archive)

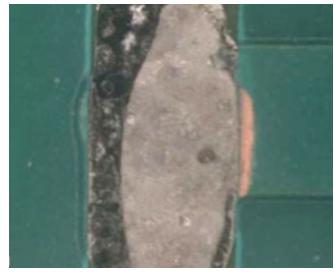

call and complains of solderability defects (Figure 5). Now the team needs to spring into action. At first glance, the fabrication team should not simply assume that the defect that manifested itself through the assembly process was the fault of the bare board. Regardless, the assembly firm most likely will not see it that way. The assembly team argued that there were issues with solder joints not forming properly—dewetting. In addition there were black areas visible across a number of surface mount pads. The final finish in question was ENIG. Now there is concern about hyper-corrosion of the underlying nickel surface.

It would be easy at this point to just call this black pad and allow the PWB fabricator to accept blame. But a truly experienced and effective troubleshooter would ask for more data and conduct additional tests on her own. One issue I sometimes encounter in cases like this is: The EMS company engineer refers the dewetting issue to IPC-610. And yes, the IPC-610 provides guidance on acceptability of wetting, etc. However IPC-610 does not provide adequate vetting in order to screen for solderability concerns or even black pad.

So, what needs to be done here is to take some of the defective boards and cross-section those areas. Refer to IPC-4552 and determine if there is corrosion of the underlying nickel. Keep in mind that minor corrosion spikes in the nickel are not cause for concern (IPC-4552).

Figure 5: Issues with assembled PWB: dewetting and black residues.

At the very minimum, the bare board fabricator must perform a thorough audit of its ENIG process including SEM analysis, gold thickness measurements and solderability testing. However, the assembly company must also provide reflow profiles, information on solder pastes used, as well as testing of the solderability of the components! Leave no stone unturned.

#### Summary: Guidelines for Effective Troubleshooting and Process Control

One of the keys to effective problem solving is a structured routine that addresses key points each time a major problem is encountered. This section suggests steps to effectively find the cause of a problem and to solve it permanently. Refer to IPC-9191 for greater detail to suggested methodology for SPC.

1. Before beginning a detailed troubleshooting project, use common sense in defining the problem.

- Verify that there is a problem

- Observe the defective product and compare it to the standard

- Identify the standard process and product, and then determine any present deviation from the standard or any change in the product

Delivering the highest quality standard for Aerospace & Defense Fully Certified AS9100 Rev C

**螣**輝雷子

Do you manufacture PCBs for the aviation, space and defense industries? With Ventec's AS9100 Rev C certification, you can rely on our fully accredited supply chain for high reliability laminates and prepregs.

From manufacture through fabrication and delivery, Ventec's high quality product portfolio of polyimides, high reliability FR4 and our range of high speed/low loss materials are all covered by the accreditation.

#### Ventec - your strategic partner for safety critical supply chains

#### Ventec International Group

China: joan@ventec.com.cn Europe: contact@ventec-europe.com USA: ordersCA@ventec-usa.com

www.venteclaminates.com

2. Establish whether operating procedures were followed and whether an assignable cause can be quickly identified as the reason behind the problem.

- Only continue into more detailed analysis if the initial questions do not lead to an obvious answer

- Even if the answer appears to be obvious, confirm the answer by operation of the process before closing the project

3. Develop a clear, concise problem statement that quantifies the problem whenever possible and reduces the scope of the investigation to a manageable size.

- 4. Gather all pertinent data and facts.

- Use SPC, historical data, records, logs, etc.

- This includes temperature charts, analysis records, maintenance logs, etc.

- 5. Perform a causal analysis.

- Producing out-of-specification parts requires immediate action (i.e., shut down the process)

- Out-of-control processes require determination as to whether the process can continue to operate

- Severe process variation requires evaluation of the severity and effect of the problem on the final product

6. Develop an action plan that includes the procedures for addressing products produced during out-of-specification or out-of-control conditions. The plan should also indicate who should make those decisions. These issues include but are not limited to:

- Disposition of the defective material (repair, scrap, replace, etc.)

- Checking the effect on scheduled delivery

- Informing the effect on scheduled delivery

- Request for non-conformance authority or material review board (MRB) action

- Establish a corrective action plan to reduce or eliminate the likelihood of recurrence

7. Conduct a measurement system evaluation, which is a means used to detect and identify the problem. This includes not only the measuring apparatus, but also:

- The sampling method

- The operator (and his/her instructions)

- Accuracy and calibration of equipment

- Environmental factors (i.e., lighting, temperature, and relative humidity)

8. The variation inherent in the measurement of attribute data and responses that are subjective in nature can be addressed. The evaluation is more complex in nature, but it is still an essential part of the analysis of the problem. IPC-9191 (General Guidelines for Implementation of SPC) discusses this subject in greater detail.

For further reading and learning on this subject, please review the IPC-9121, a new standard for understanding and preventing printed circuit board defects. This handbook provides problems, causes and possible corrective actions related to PWB manufacturing processes. To keep this document current, readers are encouraged to submit process problems with photos as well as proposed causes and solutions to the IPC 7-24 Printed Board Process Effects Handbook Subcommittee for consideration in future revisions of this document<sup>[1]</sup>:

Finally, one should never assume that making one small change in a process (new material, photoresist, specialty cleaner, etc.) does not require validation. As an example, a fabricator made a switch to another acid cleaner on its pattern plating line. The thought process was that the new cleaner (similar to the present process) would provide additional residue solubilizing properties. The result of this change was that the new cleaner attacked the sidewalls of the exposed resist, creating plating defects including copper adhesion failures and pitting. In this case the fabricator neglected the cardinal rule for considering a process change: Performing the initial capability study. These capability studies are ideally done before the process is accepted for production. This means creating a match between

# Unrivaled Speed with Full Automation

atq

### Introducing the atg A8-16a with 16 test probes at an unrivaled test speed of up to 250 measurements per second and full "lights out" Automation.

#### Get more info

| Test area:                  | 610 mm x   |

|-----------------------------|------------|

| Number of test heads:       | 16 ( 8 top |

| Smallest pad / pitch :      | 35 µm (1.4 |

| Test voltage:               | Up to 1000 |

| Max. measurements / minute: | Up to 1500 |

| Loading capacity:           | 390 mm , i |

| Max board weight:           | 20 lbs     |

| Marking option:             | Barcode la |

| 610 mm x 620 mm (24.0" x 24.4")  |

|----------------------------------|

| 16 ( 8 top + 8 bottom side)      |

| 35 μm (1.4 mil) / 80 μm (3.2mil) |

| Up to 1000V                      |

| Up to 15000 measurements /min. * |

| 390 mm , max. 80 kg weight       |

| 20 lbs                           |

| Barcode label                    |

atg Luther & Maelzer GmbH Zum Schlag 3 • 97877 Wertheim • Germany Phone +49-9342-291-0 • Fax +49-9342-395 10 sales@atg-Im.com • www.atg-Im.com the process and the product, and it results in a process control window that is capable of producing the product.

One approach to troubleshooting that quantifies improvement for reporting to management involves a capability assessment. IPC-9191 discusses in greater detail the generation of capability indices. This step promotes a clear understanding of the process matrices, but it requires time and resources. **PCB**

#### References

1. <u>Click here</u> to access an IPC Standards Improvement Form.

**Michael Carano** is VP of technology and business development for RBP Chemical Technology. To reach Carano, or read past columns, <u>click</u> <u>here</u>.

#### Solberg and Holden: Two Valuable Series Available now at I-Connect007

In early 2016, longtime author, PCB exand industry pert, veteran Happy Holden started writing a 25-chapter book, "25 Essential Skills for Engineers." He initiated it with an introductory article in the January issue of The PCB Magazine. Since that time, we have been publishing chapters approximately every three weeks in our

Happy Holden

I-Connect007 Daily Newsletter, as well as some of our weekly newsletters.

Now Happy as upped the ante. He has been writing steadily and has asked to publish every two weeks, so we said, why not? Watch for his chapters to appear every other Wednesday in the PCB section of the I-Connect007 Daily Newsletter. Chapter 4 is currently scheduled to appear on April 6. It's free to <u>subscribe</u>, so don't miss out on this highly informative and downright useful book. To catch up on the chapters we've already run, check out Happy's <u>columnist page</u> for a complete list of titles and links.

We are fortunate to have a second highlyvaluable series, penned by veteran SMT and microelectronics designer, author, and expert Vern Solberg. His six-part series, "Flex and Rigid-Flex

Vern Solberg

teristics, controlling noise, crosstalk, and impedance...saving up to 75% on space and weight... improve overall product reliability...[and] furnish unlimited freedom of packaging geometry while retaining the precision density and repeatability of printed circuits."

In part 1, Vern describes the primary flex structures, design for operating environment and base material selection. In part 2, he discusses supplier assessment, planning the flex-circuit outline and circuit routing principles, while part 3 goes into detail on specifying base materials, copper foil variations and fabrication documentation. Part 4, just published the week of March 30, focuses on rigid-flex construction, conductor routing and mechanical clearances. Part 5 is expected to publish April 27—28. Don't miss it!

Circuit Design Principles" publishes in both the <u>InsideDesign</u> and <u>Flex007</u> weekly newsletters, as well as the daily newsletter a day or so later.

Vern's introduction nicely summarizes the crux of his series: "Flexible circuits represent an advanced approach to total electronics packaging...maintain uniform electrical charac-

### GLOBAL ONLINE AUCTION: A Complete Facility Closure of a Flexible Printed Circuit Board Manufacturer

#### SCREENING AND PHOTO

- Barnaby screening table

- DuPont dry film laminator with LED and LC 2400 vacuum system

- (2) Accuprint 5KW light source

- DuPont SMVL dry film vacuum laminator

- Grieve 3X3X3 oven

- Nuarc stencil making machine

- VWR 2X2X2 dispatch oven

#### MULTILAYER

- OEM 4 opening electric press vacuum 24X30 platens

- PHI 3 opening electric press 24X30 platens

- PHI 4 opening cold press 24X30 platens

- PHI 3 opening electric press 20X18 platens

- · All separator plates used in Multilayer presses

#### DRILLING AND FABRICATION

- 5 spindle router with Saba Myra controller

- Excellon Century 2001 SP 4 spindle 180,000 Rpm Spindles

- Excellon Mark V with CNC 6 controller with 110,000 RPM spindles

- Excellon EX-200 CNC-6 2 spindles drill router 80,000 RPM spindles

- Famco 52" kick shear

- Dayton Manuel drill press

- Steel rule punch

- · All used and new drill bits

#### WET PROCESS

- Chemcut 547 XLI Etcher with main etcher, flood rinse counter flow water rinse and dryer

- Chemcut 547 Stripper strip chamber counter flow water rinse dryer

- Electroless Copper line

- 4X5X4 Copper plating tank with rectifier

- 4X5X4 Solder plating tank with rectifier

- Chemcut 547 developer with developer chamber counter flow water rinse dryer with S wheel

- Reverse osmosis waste treatment systems

- Ultra scrub scrubbing machine with extra heads

- Barrel cart mover

QUALITY CONTROL

Location: San Jose, CA

Start: April 26, 2016 / 7am PDT

Ending: April 28, 2016 / 11am PDT

• (4) Bausch & Lomb 4X microscopes

Preview: April 25, 2016 / 9am - 4pm PDT

- Leica Microscope on Nu Arc light

- Grieve 3X3X3 oven

- 2 Impulse heat sealers

- · 2 hand shear for thin material

- Stein Microscope

#### LABORATORY

- Unimet Unitron Microscope

- Mark V polisher

- Scale lab Rectifier

#### FACILITIES

- · Complete maintenance shop with all spare parts

- 2005 Scion xB Van

- (2) Kaiser Model SK 19 50 hp air compressors

- Sullivan Paletek 25 hp air compressor

- · Spencer 15 hp vacuum system with dust collector

- Back up 100 Amp generator with auto switching system

#### ADDED FROM METHUEN, MA FACILITY

- Glunz & Jensen Model ML720 Film Processor

- Universal Laser

- Blue M Model EM-606RIF Roll in Oven

- CSUN oven model CMO-8W Roll in Oven

- Tenney Environmental Chamber

- Moore Model 435 300-20 Press

- Plus more including an assortment of AL screen printing frames

#### FOR MORE INFORMATION, PLEASE CONTACT:

NICK JIMENEZ 203.733.7191 NJIMENEZ@HGINC.COM

JUST ADDED: Plasma System Model 1400

#### www.hgpauction.com

### **MilAero007** Highlights

#### FTG Circuits Qualified to MIL-PRF-31032

The FTG Circuits, Chatsworth, California facility has been qualified to the Department of Defense performance specification MIL-PRF-31032/3 (flexible printed wiring boards) and MIL-PRF-31032/4 (flex-rigid printed wiring boards).

#### API Technologies to be Acquired by PE Firm

API Technologies Corp., a leading provider of high-performance RF, microwave, millimeterwave, power, and security solutions, announced a definitive agreement providing for the company to be acquired by an affiliate of private equity firm J. F. Lehman & Company (JFLCO), which specializes in the aerospace, maritime and defense industries.

#### PCi Purchases Polar CITS880s Controlled Impedance Tester

Rigid flex circuit board manufacturer, Printed Circuits Inc., purchased a CITS880 controlled impedance tester from Polar Instruments. Polar Instruments' software and testing equipment is the most popular solution in the PWB manufacturing industry for predicting and verifying controlled impedance circuits in circuit boards.

#### BAE Systems, Shengyi Receive IPC Corporate Recognition Awards

IPC – Association Connecting Electronics Industries bestowed its highest corporate honors to two member companies, BAE Systems and Shengyi Technology Co. Ltd. During a luncheon at IPC APEX EXPO, the IPC Stan Plzak Corporate Recognition Award was presented to BAE Systems and the IPC Peter Sarmanian Corporate Recognition Award to Shengyi Technology Co. Ltd.

#### PrecisionHawk Explores Extreme-Weather Testing of Drones at ACE

PrecisionHawk has successfully completed the world's first extreme-weather testing of unmanned aerial vehicles (UAVs) in the ACE climatic wind tunnel at the University of Ontario Institute of Technology (UOIT).

#### Robots: Eliminating the First Contact with an Enemy Force

"We should be thinking about having a robotic vanguard, particularly for maneuver formations," said Dr. Bob Sadowski. "There's no reason why the first contact with an enemy force should be with a man-platform, because it means that platform is at the greatest risk."

#### PNC Purchases Universal Pick and Place Equipment

Sam Sangani, president and owner of PNC, has announced that his company recently added a new Universal pick and place machine, model Genesis GI-07, to its fast-growing assembly department.

#### Configurable Analog Chip Computes with 1,000x Less Power than Digital

Researchers have built and demonstrated a novel configurable computing device that uses 1000x less electrical power—and can be built up to 100 times smaller—than comparable digital floatinggate configurable devices currently in use.

#### IPC APEX EXPO 2016: Glenn Oliver on His IPC "Best Paper" on High-Frequency Materials

Glenn Oliver of DuPont discusses his award-winning paper, "Round Robin of High-Frequency Test Methods by IPC-D24C Task Group." Co-authors include Jonathan Weldon of DuPont, John Andresakis of Park Electrochemical, Chudy Nwachukwu of Isola, John Coonrod of Rogers Corporation, David L. Wynants of Taconic Advanced Dielectric Division, and Don DeGroot of Connected Community Networks.

#### Harris Signs Definitive Agreement to Sell Aerostructures Business

Harris Corporation and Albany International Corp. today announced a definitive agreement under which Albany International will acquire Harris' aerostructures business for an enterprise value of \$210 million, including \$187 million in cash at closing and the assumption of a \$23 million capitalized lease.

# **SILVER Lining...** Priced with the market COOLSPAN® TECA thermally & electrically conductive adhesive

COOLSPAN® TECA Film provides an easy solution to solving your thermal management challenges. Available directly from Rogers Corporation, without the middleman, COOLSPAN TECA is supported by Rogers' technical staff to help you gain the best result from this environmentally stable conductive adhesive. Keep your cool and maintain your budget.

- · Epoxy-based Adhesive Film

- · Market Priced to Silver Spot Price

- Excellent Thermal & Electrical Properties

- · Predictable Flow

- · Durable & Reliable

Contact Rogers Corporation for more information or to request a sample USA - AZ, tel. +1 480-961-1382 • EUROPE - BELGIUM, tel. +32 9 235 3611

**SILVER MARKET PRICE**

CORPORATION

Advanced Connectivity Solutions www.rogerscorp.com/COOLSPAN

# Process Management: Doing It Right

#### by Todd Kolmodin

GARDIEN SERVICES USA

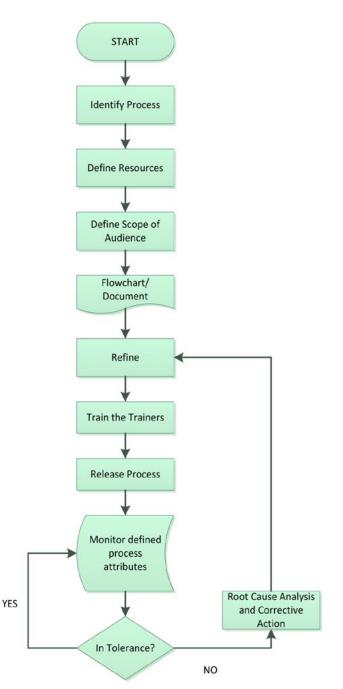

The term "process management" is widely used in today's economic theatre, but what is it really? Simply put, it is the idea of figuring out how to do something, documenting it and then monitoring the effectiveness of the steps you created for the end result. Simple, right?

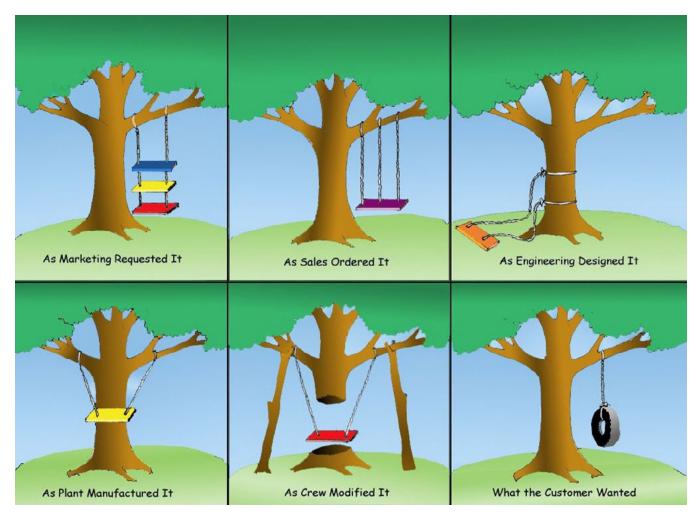

Unfortunately, many who take on this endeavor fall short due to missing some key attributes to creating and maintaining a robust process. It doesn't matter whether we are building a box or building a battleship, the theories are the same. Many consider writing work instruction the process but it is only one of the key attributes. Remembering this will no doubt keep you from the pitfalls of process failure. We all remember what the customer wanted, right?

A process that is unclear when created will undoubtedly result in something like the picture in Figure 1. So let's build a process correct-

Figure 1: How not to communicate.

# ENTER THE JET AGE

#### INKJET PRODUCTS RIGID AND FLEXIBLE

- 😵 Bright White Legend Ink

- IJR-4000 Series

- IJR-4000 FW100

- 🗑 Solder Mask

- IJSR-4000 Series

IJSR-4000

IJR-4000 FW100

IJR-4000 MW300

Phone [775] 885-9959 • www.taiyo-america.com • info@taiyo-america.com

ly. There are eight steps in building and maintaining a robust process:

**1. Identify the process.** What are we trying to do? This may sound a bit general, but it is critical. Write it down.

**2. Determine the resources needed for the process.** If we are building a box we will need materials such as wood, nails, screws, a hammer, etc. Determine what tools will be needed to create what we defined in Step 1.

**3. Decide who is doing it.** This is a critical step that many overlook. Who is going to be doing this process? In many cases, the mistake is that the process is written so overly technical that only a Ph.D. or rocket scientist could possibly understand. This leads to breakdown and ultimately, process failure. Now if the process requires a Ph.D. or rocket scientist to perform the steps then by all means write it and include the attributes required for that audience.

4. Create a flowchart/diagram. Now it's time to document your actual steps. This may include more than one document if more than one department or entity is involved. This is your work instruction phase. This is best documented while the actual steps are being performed. It is much more difficult to look at the finished product in a conference room and reverse-engineer by memory. Do it hands-on. It will save edits and missed steps in your process. This is a time to again consider your audience. While in this phase, reflect on what is critically needed for the process and what may be left out if some common knowledge is already indicated.

**5. Expand.** Now that you have your steps, review each one and expand if necessary to include specifics about a given step. Perhaps a special tool is required in one step or a certain color of paint. This is the time to provide examples. What should the product or activity look like at a certain step? Visual examples work very well to gauge whether the process is developing the desired result. Be careful during this step as to not write yourself into a corner. Consider the future and other integrated processes

Figure 2: Process-building steps flowchart.

that may work with yours. If your process is too tight, you may have issues with amendments or changes in the future, or have issues modifying your process to accommodate a sister process related to your own.

**6. Test the process document.** If you wrote it, I don't mean you. Find a volunteer to read

# POWERED BY SCIENCE...

and Industry's

**Best Technical**

Team

UYEMURA

**USA**

Pat Valentine

Don Gudeczauskas

#### Uyemura PCB finishes are best in class...

... but our greatest strength is our technical team. UIC field and development specialists have an average of 26 years in the PCB industry, and a wealth of knowledge about how to make your shop succeed on all levels.

#### ENIG

Al Gruenwald

George Milad

John Meyers

Jon Bengston

The industry standard for producing uniform mid-phos EN deposits with a thin topcoat of immersion gold, over copper. Solderable and aluminum wire bondable; no dummy plating.

#### ENEPIG

Only UIC has multiple options - alloyed and non-alloyed palladium baths - so you can choose for highest stability, greatest speed, substantially improved diffusion layer for optimized corrosion protection, widest processing window.

#### Via Fill Coppers

Including EVF-N, which simultaneously plates through-holes and blind vias (even those smaller than 150 µm), reducing process time by 50%.

www.uyemura.com

Rich DePoto

Mark Eonta

through the document and perform the steps within. Here you will find where something may have been accidentally omitted. Make your correction(s) and do it again using a different volunteer. When you are satisfied with the results it's time to move to the next step.

7. Train the trainers. I can't emphasize this enough. Here is one of the biggest failure mechanisms in process management. You just created a great document and released it to production and you can't figure out why it's not working! Whether your organization is large, with training staff, managers and operators or just a small shop, the focus must be the same. You must train who will be performing the process. Whether it is a workshop-type training session or a one-on-one meeting, you must go through the steps, listen to questions and document who, what, where and why. This is part of your process management: accountability. If there are many sub-processes involved in your final desired outcome (box or battleship) this must be done for each individual sub-process. Don't skip or cheat this step or you will have undesirable results and difficulty finding the root cause of any failure.

**8. Monitor.** Of all the steps, this final step is the most important. How do you know if the process you created six months ago is still as strong today as it was the day you created it?

You need to have your finger on the pulse of that process. How do you do that? Define inspection steps or key objectives to be monitored during the process. Define limits to those attributes and instructions when a control is violated. Doing this can provide immediate attention to the faulting occurrence whether it be equipment, human or unknown at the time. Utilizing '5 Why' root cause analysis can ultimately isolate the out-of-control root cause and you can then correct it but that's for another day.

To conclude, when building and maintaining a process, don't be overwhelmed by the overall scope of the final required result. While some processes may be very large with many integral steps we can break each of these down using the eight steps. These building blocks can then be unified to capture the entire desired result while also monitoring each phase for any out of control conditions that may affect the final result. Use the process building step flowchart to guide you to successful process building. **PCB**

**Todd Kolmodin** is the vice president of quality for Gardien Services USA, and an expert in electrical test and reliability issues. To read past columns, or to contact Kolmodin, <u>click here</u>.

### Couldn't make it to the March Show(s)? Catch Up with Real*Time with...*Coverage!

March was *huuuuuge* for important industry events this year, with IPC APEX EXPO 2016 in Las Vegas, Nevada, and CPCA 2016 in China the very same week. I-Connect007's Real*Time with...* video crews were at both locations, on opposite sides of the world. The result is more

than 100 excellent videos that put you right on the show floors where you can learn about the newest equipment, the latest in processing, industry trends, market analyses, and so much more. Watch the videos from IPC APEX EXPO <u>here</u>, and see the CPCA videos <u>here</u>.

In addition, our roving reporters talked with speakers, exhibitors, attendees, and movers and shakers in the industry. These transcribed audio interviews are publishing NOW in our

<u>I-Connect007 Daily Newsletter</u> and in our weekly newsletters. <u>Subscribe today</u> to receive these straight to your inbox.

Thursday, May 12th, 2016 3:00pm - 8:00pm Irvine, Calif. Marriott Interested in sponsoring? Contact us here.

Calling all **West Coast Geeks...** this year we have expanded our event to Orange County... **be there because you** *are* **square!**

Check out this short drone video of last year's event in Minneapolis where we hosted over 300 attendees.

Learn more at: tntgroup.org

### Join us May 12th to:

- Network with peers from all aspects of the electronics community

- Enjoy good food and music

- Meet new friends and catch up with old ones (well not *THAT* old!)

- Learn about the latest and greatest products and technology

- Connect with industry suppliers in a relaxing atmosphere

#### We look forward to seeing you!

EXCLUSIVE MEDIA SPONSOR

## **Focusing on What Matters Most!**

#### by Renato Peres CIRCUIBRAS

Every company claims to be constantly improving their business or process, but not as many grasp the core idea of continuous improvement and live it daily. This is evident when one analyzes companies competing on the same market, providing quite the same products, yet having totally different results. Improvement is often misunderstood as doing things differently, which is a huge mistake.

Taiichi Ohno was known as the father of the Toyota Production System, helping Toyota to become the best automaker in the world. In the '80s, another engineer and scientist working at Motorola, Bill Smith, had just started a revolutionary culture change at his company. At that time, Motorola was struggling to compete against its rivals, which delivered better products with lower prices. A simple tool wouldn't help them to succeed. They needed a change in their business strategy.

Bob Galvin, who had just stepped down as CEO of the company in 1986, was so amazed by Smith's belief in Six Sigma that he made it a strong component of Motorola's culture.

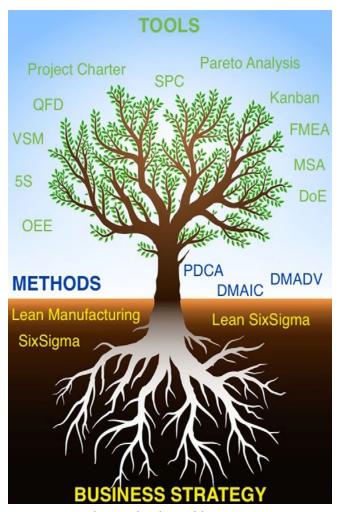

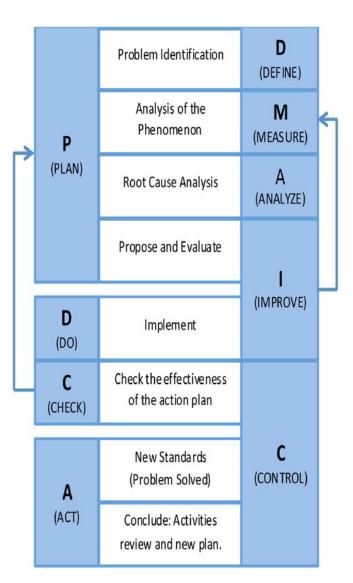

Since then, Six Sigma has gone through several changes including the substitution of its primary method MAIC (measure, analyze, improve, control) for DMAIC (define, measure, analyze, improve, control). Most recently, it has added the Lean manufacturing practice and philosophy, giving birth to the Lean Six Sigma strategy.

In both cases, the success of the change in business strategy and culture was due to a topdown initiative, and this is a point we should not overlook. I have no doubts that if you just use the tools or methods that are part of Six Sigma or Lean manufacturing, you will get satisfactory outcomes. However, spectacular results will be determined by the deep commitment of the top management.

With this is mind, l will present a quick overview on DMAIC methodology, which is

#### 1798: Eli Whitney, Mass Production and Interchangeable Parts

- Need for consistency.

- · Identification of defects.

#### 1924: Walter Shewhart

- · Process oriented thinking.

- · Control charts (assignable and common cause).

#### **1945: The Japanese Quality Movement Begins**

- · Statistical methods and use of statisticians.

- Continuous improvement (plan-do-study-act) methodology.

- Active engagement of management and involvement of everyone.

- · Diagnostic and remedial journeys.

#### 1973: The Japanese Make Their Move

• Quick responce to changing customer needs.

#### 1980: Philip Crosby and Quality Is Free

- Methodology to achieve companywide quality improvement.

- Improve product, process and service. Strive for perfection.

#### **1987: International Organization for Standardization**

- Widespread sharing of basic elements of sound quality systems.

- Organizational rally cry for improvement.

#### **1987: Malcolm Baldrige National Quality Award**

- · Sharing best practices.

- Strong focus on customers and results.

#### 1987: Motorola and Six Sigma

- Focus on customer needs and comparison of process performance to those needs.

- Structured methodology with discipline and proven business results.

#### 1960-1995: Other Initiatives

• Tools to be used by everyone in the organization.

Figure 1: Six Sigma history<sup>[1]</sup>.

www.gardien.com

Global Quality Assurance Solutions tailored to your individual needs

#### Click here for more information about all of Gardien's services

## Building HDI Fixtures with Test Pins Smaller than a Human Hair

Electrical Testing Fixturing 4WK, Hi-Pot, Impedance Testing CAM and CAD Services Final Visual Inspection Automatic Optical Inspection Automatic Visual Inspection Equipment Sales and Service Consulting one of the pillars of Six Sigma, and may help you answer questions like:

- How do you know you have improved your process?

- Have you seen better results since last week, month, or year?

- Do you still maintain the results you have achieved?

- Did you or your team help your company to achieve its goals?

- How much money has your company saved?

DMAIC methodology gathers several tools we all have heard about, such as: Pareto analysis, value stream mapping, failure mode and effect analysis, statistical process control, and

Figure 2: Tools, methods and business strategy.

project charter, to cite some. But it goes further, creating a meticulous path to execute the activities presented on the method, which results in correct conclusions of what must be done.

#### Define

Everything starts here, and it is said that if you start well, you may finish well.

At this point, it is very important to clearly DEFINE what are the goals and scope of the project.

Remember, the methodology is not only about process improvement, but improving your company's outcome. So it is necessary to make it clear that the goal you set here must be in accordance with your company's goals.

Sometimes, engineers (myself included) want to make excellent that which may not be financially good for the company. If you allow me to offer a piece of advice, keep the focus on the golden pot: customer and money. And always discuss your project with top management.

According to Vicente Falconi Campos, a well-known Brazilian business consultant and writer, a target consists of a management goal, a value, and a deadline. Keep it in mind.

Here are some tools that may guide you through the definition of your goals:

Project charter; financial analysis; voice of the customer (VOC); and value stream mapping (VSM).

#### Measure

Data is as essential to Six Sigma as the air we breathe. If you want to know what you have improved since last semester, you need to know where you were last semester. Thus, work hard to establish the baseline and the targets for each problem. If you don't have any data, or just have poor data, you will need to plan how to collect new data.

Statistical tools and techniques are widely used on this step: histograms, control charts, boxplots, and Pareto analysis, along with VSM and measurement system analysis (MSA).

#### Analyze

"Give me six hours to chop down a tree and I will spend the first four sharpening the axe." — Abraham Lincoln

# **Flex Drilling and Cutting**

5000

LPKF MicroLine

The MicroLine 5000 is the flex PCB industry answer to high through-put, high-yield drilling applications. With the ability to drill holes down to 20µm, a variety of both organic and inorganic substrates can be processed, such as:

Flexible PCBs

- High Density

- IC Substrates

Interconnect PCBs

Laser & Electronics

### 1-800-345-5753 www.lpkfusa.com/flexdrilling

Determining the root cause of the problems identified in the first step is the goal here. This is the last step before you go into action.

Not thoroughly analyzing the root cause will compromise the whole process, because it will drive you to wrong actions. My suggestion: Don't waste your company's and your teams' precious time and money; do your best to get to the root cause.

Some of the tools you may use to achieve your goal include: Eight Disciplines Problem Solving (8D Analysis), 5 Whys, Fishbone Diagram, Brainstorming, Failure Mode and Effect Analysis (FMEA), and Cycle Time Analysis.

#### Improve

The goal is to come up with ideas to eliminate the fundamental causes of the problems defined (propose), analyze the risk of each action (evaluate) and test the chosen solutions (implement). After testing, it is necessary to check the results and go back to the measure step if necessary.

#### Control

It seems obvious, but leaders may fail on this step. Have you ever had the feeling that you had already faced a specific problem? If so, it is because the method hasn't come to an end yet. In order to preserve the results, new patterns must be defined and shared through all the organization. A training section must be done, as well as the updates of all your manuals and work instructions. If possible, use automatic devices or methods to prevent failure to occur (Poka-Yoke).

#### Conclusion

It is not uncommon to see people focused on doing things that are urgent, and sometimes not important and solving immediate problems instead of thinking of the long term. Here in Brazil we have an idiomatic expression for that: "apagar incêndio," which literally means working to extinguish a fire instead of preventing it from happening.

DMAIC works to extinguish the fire and prevent it from happening again.

For more information on Six Sigma visit the website isixsigma.com. **PCB**

Figure 3: PDCA and DMAIC<sup>[2]</sup>.

#### References

1. The Evolution of Six Sigma by Jim Folaron, J.P. Morgan Chase & Co, August 2003. 2. Métodos PDCA e DMAIC e Suas Ferramentas Analíticas by Cristina Werkema.

**Renato Peres** is an industrial engineer and production coordinator with Circuibras Circuitos Impressos Profissionais.

### **FCM 30** DRY FILM AUTO CUTTING LAMINATOR

Ergonomic Touch Screen

Sliding access door

-

External mount chain drive

Easy roller cleaning

The leading European PCB Equipment and Parts Supplier

www.vikingtest.com sales@vikingtest.com

#### Outstanding Group of Companies and Individuals Receive FlexTech's FLEXI Awards

FlexTech, a SEMI Strategic Association Partner, awarded five FLEXI Awards in the categories of Innovation, Research & Development, Leadership in Education, and in a category new this year, Industry Leadership.

#### Insulectro Debuts Shikoku New Chemistry Supplier at IPC APEX 2016

Insulectro, a leading supplier of materials for use in the PCB and printed electronics industries, will introduce a new supplier, Shikoku Chemicals Corporation, at IPC APEX EXPO to augment its highly successful chemistry line.

#### ITL Circuits Invests in Excellon COBRA Hybrid Laser System

Excellon is proud to announce the sale of a COBRA Hybrid Laser System to ITL Circuits in Markham, Ontario. The installation is scheduled for early second quarter of this year.

#### Speedy and Metro Circuits Install New Chemcut CC 8000

Chemcut Corporation, the United States' leading manufacturer and supplier of develop/etch/ strip equipment, announces that PJC Technology Inc., DBA Speedy Circuits and Metro Circuits, have both installed new Chemcut CC 8000 cupric chloride develop-etch-strip systems in their facilities.

#### Atotech Opens a New Chemical Plant in Penang

With an initial investment of RM 50 M, the new facility will cater to the growing demand of Atotech's solutions in South East Asia.

#### LPKF Launches Entirely New Flex Drilling & Cutting Laser

Electronics manufacturing equipment manufacturer and laser specialist LPKF Laser & Electronics AG is launching an entirely new laser drilling and cutting system specifically tailored to the needs of the flexible circuit industry.

#### Insulectro Promotes Michelle Walsh to Director of Product Management

Insulectro, a distributor of materials for use in the printed circuit board and printed electronics industries, has promoted long time associate Michelle Walsh to director of product management.

#### Viking Test Unveils Expansion Activities

Viking Test moved to new UK headquarters facility. The new facility with 15000 sq. space gives Viking enough opportunity to accommodate current workload and future expansion plans.

#### Insulectro Hires Industry Vet Chris Hrusovsky as VP of Sales for Chemistry

Insulectro has hired industry leader Chris Hrusovsky as VP of Sales for Chemistry. "I am pleased today to announce Chris Hrusovsky has joined the Insulectro family," commented Patrick Redfern, president of Insulectro.

#### Catching up With Tom Hausherr of PCB Libraries

When fate placed Tom Hausherr and me at PCB West, we made sure to carve out some time together. Tom agreed to have a long breakfast with me so I could learn more about the challenges related to component libraries and how his company addresses these issues. So, pull up a chair and join us for a chat.

LCOA's CONFORMAT™ ... soft enough to overcome image transfer challenges, hard enough to suppress exit side burrs

Some things are better at adapting than others.

- Revolutionizing the drill room

- Adapts its shape to fill irregularities

- Prevents burrs on panels with image trasnfer

- Minimizes board rework

## **Flexible Circuits and Kaizen Events**

#### by Dave Becker ALL FLEX FLEXIBLE CIRCUITS LLC

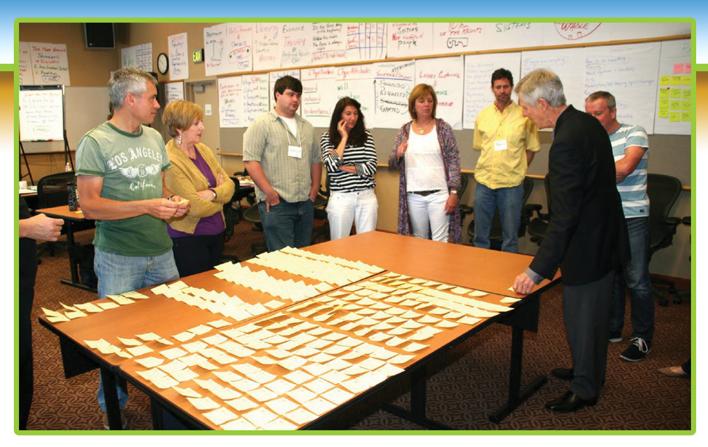

All Flex uses a variety of different tools and techniques in its continuous improvement efforts. A Kaizen event or Blitz is one technique that has resulted in significant improvements in our yields, productivity and customer satisfaction. A Kaizen event is a short-term effort using a dedicated team that is highly focused on improving a narrowly defined process. Kaizen teams usually consist of 3–8 members that include operators, engineers and other support personnel. The implementation phase of the event usually lasts 3–6 working days and the team members are removed from their daily duties to focus 100% of their time on the Kaizen effort.

A Kaizen event is highly structured, and while the exact steps may vary from project to project, the process consists of three phases:

- Planning and preparation

- Implementation

- Follow-up and tracking

Action items, analysis and recommendations are formally documented during each phase. The first step is to select and define the project. Kaizen events, as well as other improvement efforts, are selected based on a Pareto analysis that is presented to the management team. Selection is based on the process improvement that would have the biggest impact on one of the following:

- Scrap

- Throughput

- Quality

- Customer satisfaction

The planning and preparation phase of a Kaizen blitz can take 2–6 weeks. During this phase, the project charter is defined, a team is chosen, data collected and project orientation is performed. The Kaizen event can be disruptive, so the affected departments need to plan on how to deal with the potential disruptions.

**TECHNICA, U.S.A.** Fulfilling Manufacturing Needs Throughout the Electronics Industry

## **Chemstar: A Versatile Solution**