an IConnect007 publication

The Top 10 Ways Designers can Increase Profits p.10

Design Strategies for Success—and Profit p.16

The Need for Speed: Strategies for Design Efficiency p.22

for innovatio

base

Much More!

# **Strategies to Increase Profit**

### The Top 10 Ways Designers Can Increase Profits

by Mark Thompson, pg. 10

# **PCB BUYERS**compare nearly 1900 manufacturers now at The PCB List.

**Quick Search**

Advanced Search

The best way to find a PCB fabricator, anywhere.

#### www.thepcblist.com

Thursday, May 12th, 2016 3:00pm - 8:00pm Irvine, Calif. Marriott Interested in sponsoring? Contact us here.

Calling all **West Coast Geeks...** this year we have expanded our event to Orange County... **be there because you** *are* **square!**

Check out this short drone video of last year's event in Minneapolis where we hosted over 300 attendees.

Learn more at: tntgroup.org

#### Join us May 12th to:

- Network with peers from all aspects of the electronics community

- Enjoy good food and music

- Meet new friends and catch up with old ones (well not *THAT* old!)

- Learn about the latest and greatest products and technology

- Connect with industry suppliers in a relaxing atmosphere

#### We look forward to seeing you!

EXCLUSIVE MEDIA SPONSOR

#### **March 2016**

# **UESION** Feature Content

Designers have a plethora of ideas about how to best layout a PCB. But how many designers understand that good design techniques can lead their company to greater success, and even profit? In our cover story, Prototron's Mark Thompson offers 10 design strategies that can help your bottom line. We also feature articles on profitable design strategies by Gary Griffin of Fast Interconnect and Barry Olney of In-Circuit Design Pty Ltd. And we round out this issue with interviews with Nolan Johnson of Sunstone Circuits and Greg Roberts of EMA Design Automation.

- **10 The Top 10 Ways Designers Can Increase Profits** *by Mark Thompson*

- **16 Design Strategies for Success—and Profit** *by Gary Griffin*

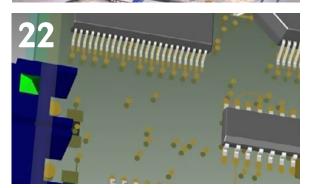

- 22 The Need for Speed: Strategies for Design Efficiency by Barry Olney

# **185HR** High-Tg, Low-CTE Materials with High Thermal Reliability

#### **FEATURES**

- High Thermal Performance

- Tg: 180°C (DSC) (Base Laminate)

- ▶ Tď: 340°C (TGA @ 5% wt loss)

- Low CTE for reliability

- T260: 60 minutes

- T288: >15 minutes

- · Lead-free Compatible and RoHS Compliant

- UV Blocking and AOI Fluorescence

- High throughput and accuracy during PCB fabrication and assembly

- Superior Processing

Closest to conventional FR-4 processing

- Industry Approvals

- IPC-4101D-WAM1 /98 /99/ 101 /126

- UL File Number E41625

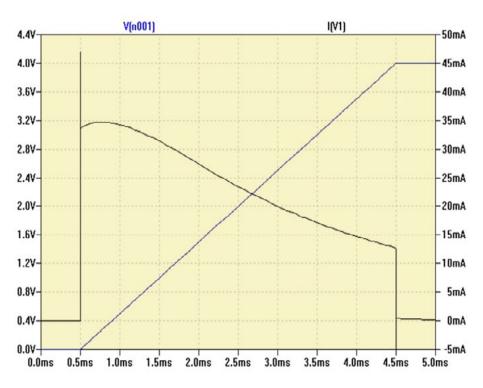

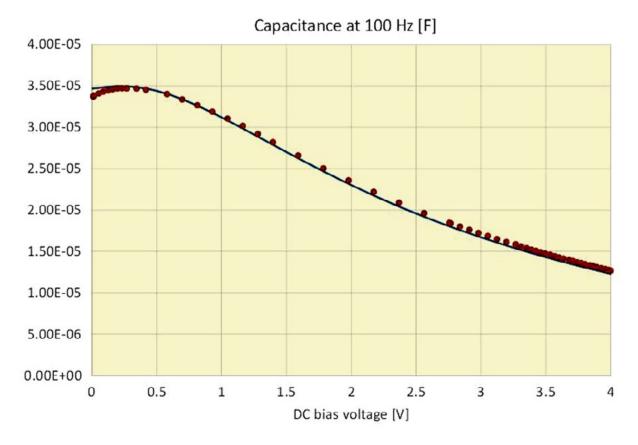

- Qualified to UL's MCIL Program

#### **KEY APPLICATIONS**

- Heavy copper, 6 & 12 oz automotive applications

- Military

- Medical

- Industrial

- · Core Material Standard Availability

- Thickness: 0.002" (0.05 mm) to 0.060"/0.062" (1.5 mm)

- Àvailable in full size sheet or panel form

- Prepreg Standard Availability

- Roll or panel form

- Tooling of prepreg panels available

- Copper Foil Type Availability

- Standard HTE Grade 3

- RTF (Reverse Treat Foil)

- Copper Weights

- ½, 1 and 2 oz (18, 35 and 70 μm) available

- Heavier copper available upon request

- Thinner copper foil available upon request

#### · Glass Fabric Availability

- Standard E-glass

- Square weave glass fabric available

#### **ORDERING INFORMATION:**

Contact your local sales representative or visit www.isola-group.com for further information.

Isola Group 3100 West Ray Road Suite 301 Chandler, AZ 85226 Phone: 480-893-6527 info@isola-group.com

Isola Asia Pacific (Hong Kong) Ltd.Isola GmbHUnit 3512 - 3522, 35/FIsola StrassNo. 1 Hung To Road, Kwun Tong,<br/>Kowloon, Hong KongD-52348 Dür<br/>Phone: 49-2Phone: 852-2418-1318info-dur@isinfo.hkg@isola-group.comIsola Strass

Isola GmbH Isola Strasse 2 D-52348 Düren, Germany Phone: 49-2421-8080 info-dur@isola-group.com

#

**March 2016**

Vol. 5, No. 3

thepcbdesignmagazine.com

#### SHORTS

- 36 Step Towards 'Holy Grail' of Silicon Photonics

- 40 Plasma Processing Technique Takes SNS Accelerator to New Energy Highs

- 47 MaXphone to Bridge Handheld Radios and Smartphones

- 63 Robots: Eliminating the First Contact with an Enemy Force

- 74 Researchers Develop Highly Efficient Hollow Copper Electrodes

#### DEPARTMENTS

- 78 Events Calendar

- 79 Advertisers Index & Masthead

# **More Content**

#### ARTICLES

- 60 EMA is Bullish on Data Management Interview with Greg Roberts

- 64 Sunstone Circuits R&D: 3D Printing Great for Prototyping Interview with Nolan Johnson

- 70 The Gerber Guide, Chapter 7 & 8 by Karel Tavernier

#### COLUMNS

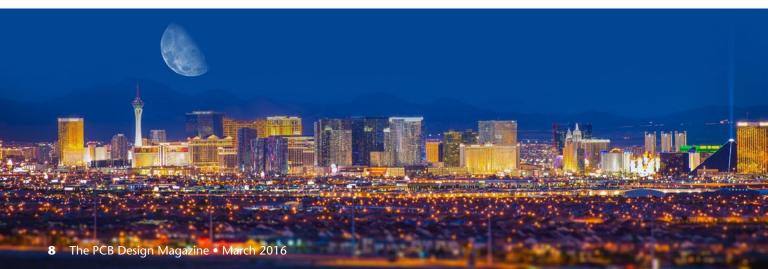

- 8 Back to Vegas by Andy Shaughnessy

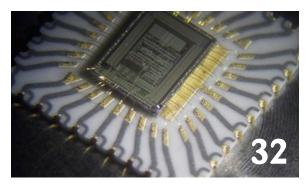

- **32** The Principles of Hybrid Design, Part 1 by Tim Haag

- **38 Design and Production: Some Essential Facts** *by Phil Kinner*

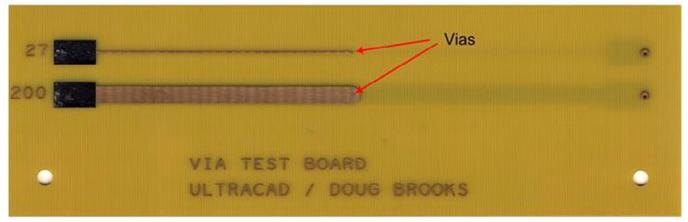

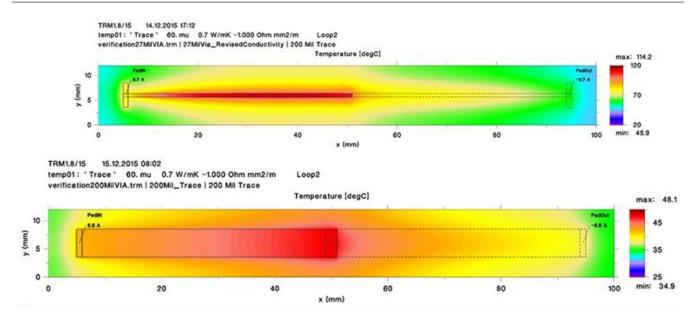

- **42** How Many Vias Does It Take To...? by Douglas G. Brooks

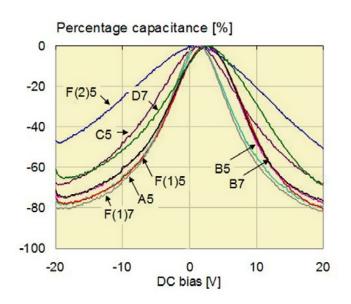

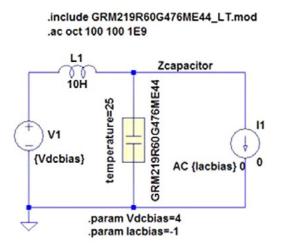

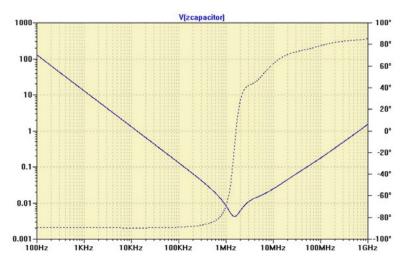

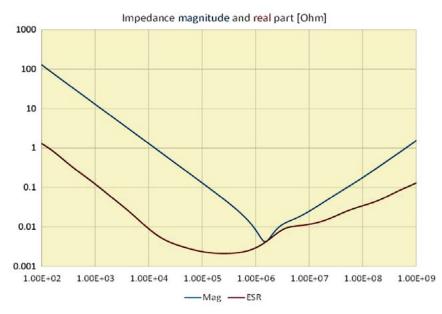

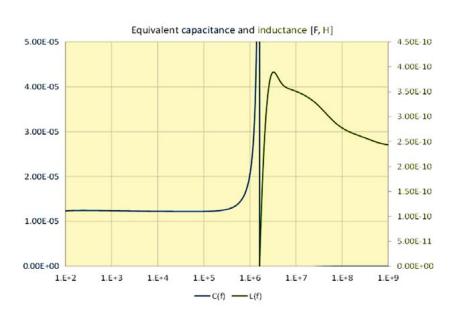

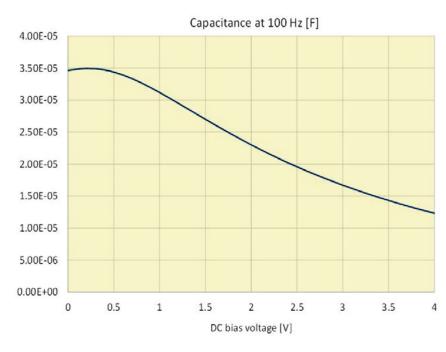

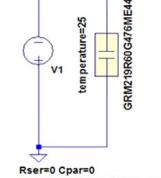

- 48 Dynamic Models for Passive Components by Istvan Novak

#### HIGHLIGHTS PCB007

30

- 56 MilAero007

- 76 Top Ten PCBDesign007

# PCB Fab & Assembly Services from China's Experienced Manufacture

#### More professional | More reliable | Quick turnaround | Less cost

#### **New Customer Offer** Claim Now» Save **15%**, up to \$200 OFF Use Code: **PCBDE007**

#### Our advantages -

- ☑ Fully ISO9001:2008, UL and RoHS certified

- ☑ Pro-PCB fabrication up to 32 layers

- Prototype to production

- Min. tracing/spacing to 3mil/3mil

- ☑ Min. microvias to 0.1mm

- Special PCBs-Aluminum, Flex & Rogers PCBs, etc.

- Small Qty full turnkey PCB assembly

www.pcbcart.com

sales@pcbcart.com

+86-571-87013819

# **Back to Vegas**

by Andy Shaughnessy I-CONNECT007

It's almost time to head back to Las Vegas for IPC APEX EXPO, along with my favorite event, the Design Forum. I'm glad to be heading back to the land of Lost Wages, and in a new venue, the Las Vegas Convention Center. The last time I attended a trade show in the convention center was in the summer of 2001 for the Design Automation Conference.

DAC was held in June that year; who had that bright idea? I guess the surface of the sun was booked! That year, I perfected the art of "shade darting," running from one bit of shade to the next. It was 108° the entire week of DAC 2001, and it was so hot that the cab drivers almost turned on their air conditioning. Let's hear some applause for IPC not holding APEX in Vegas during the summer months.

So we're back in Vegas again. But I've heard grumbling from people in the electronics industry who are worried that attendance is going to drop off this year. You've heard the traditional arguments for holding APEX in San Diego vs. Las Vegas: There are hundreds of circuit board companies and defense contractors in and around San Diego, the weather is perfect, and your manager is more likely to sign off on a visit to San Diego than Vegas. IPC knows this, of course, and I understand that they'll be holding APEX in San Diego in 2017 and for several years after that. You can't please everyone.

The I-Connect007 team will get to Vegas over the weekend and start planning our wallto-wall coverage. I get started early in the week with my coverage of the Design Forum on Monday, March 14. Anne Marie Mulvihill and her accomplices at IPC have set up a solid design program. The subtitle of Dale Parker's keynote speech offers a hint of what you can expect: "Brother, Can You Par-a-Digm?" Parker is the eCAD tools and support manager for Google/ Alphabet, and he'll be discussing "Paradigm Shifts Required to Accomplish Next-Generation Technical Innovation."

Next, Gary Carter of Fujitsu, Humair Mandavia of Zuken, and Hemant Shah and Ed Acheson of Cadence Design Systems will present "Seamless Data Transmission from Design through Assembly: Briefing from the IPC-2581 Consortium." Speaking of which, if any of you are using IPC-2581 on a regular basis, I'd like to hear about your experience. Have you ever designed a PCB using this neutral data transfer standard?

Then, Karen McConnell of Northrop Grumman, Dock Brown of DfR Solutions, and Dale Lee of Plexus will discuss "Developing a DFX Program for Your Organization: DRC in a Layout Tool vs. DFX Rules When Checking a Board." That sounds like a great session; Karen is a hoot, as well as a great instructor. Cherie

Figure 1: Kelly Dack, PCB designer, gentleman farmer and novice cattleman.

Litson of Litson Consulting follows with "New Developments in IPC Industry Standards: A Review of Key Issues for Design Teams," and our own columnist and technologist Vern Solberg of Solberg Technical Consulting updates us on IPC-7091 and 7092 with his talk, "2D, 2.5D and 3D Package Technology: Embedded Component and Advanced Semiconductor Package Innovation."

With so much talk about the need for (and lack of) good communication between designers and fabricators, "Making Your Design-Fabrication Collaboration Most Effective" should draw a good crowd. Mike Creeden of San Diego PCB will be joined by contributors Tom Clifford of TJB Associates and Phil Marcoux of the Fab Owners Association. And rounding out the Design Forum is a presentation by Stephen Chavez of UTC Aerospace Systems and Scott McCurdy of Freedom CAD, "Continue Your Professional Development with IPC Design Programs, Technical Education and Networking."

It sounds like a great Design Forum. I'll be there bright and early Monday. Unfortunately, our guest editor and contributor Kelly Dack won't be with us at APEX. Kelly is taking delivery of seven head of cattle next week. No, Kelly does not know anything about cattle; he's from Southern California. He never even lived on a farm until he moved to Spokane, Washington this year. Let's wish Farmer Kelly luck with his efforts at animal husbandry!

#### **Profitable Design Strategies**

We have a great issue for you this month. We're focusing on design strategies that can lead your company to success, and profit. Yes, as Mark Thompson of Prototron explains in our cover story, even the "lowly designer" has some control over the company's bottom line. And we have feature articles on profitable design strategies from Gary Griffin of Fast Interconnect and Barry Olney of In-Circuit Design Pty Ltd.

We also bring you interviews with Greg Roberts of EMA Design Automation and Nolan Johnson of Sunstone Circuits, as well as contributions from columnists Tim Haag, Phil Kinner, Doug Brooks and Istvan Novak.

I better wrap it up and get my clothes to the dry cleaner. I hope to see you at IPC APEX EXPO and the Design Forum. If you can't make it, don't worry; we'll be covering the show from start to finish. **PCBDESIGN**

**Andy Shaughnessy** is managing editor of *The PCB Design Magazine*. He has been covering PCB design for 16 years. He can be reached by clicking here.

# The Top 10 Ways Designers Can Increase Profits

#### by Mark Thompson, CID PROTOTRON CIRCUITS

Some of you are probably wondering about the title of this article. "What could Mark possibly mean? How can a lowly PCB designer like me increase our company's profits?"

So can you truly increase profitability through PCB design practices? Yes, you can. And it starts with a philosophy that embraces DFM techniques. Then you must be ready for the initial release to a fabricator by ensuring that you are communicating all of your specifications and needs clearly to the fabrication house so that you get an accurate quote.

Let's dive in, starting with Number 10 and working our way to the most important way a designer can increase company profits.

#### **10.** Accurate Fab Notes

I cannot over-stress this one. Lets talk about some common fab notes that can cause confusion, sometimes delaying your quote.

For instance, do copper weights refer to starting or finished weight? A standard note may read, "All copper weights listed on the stack-up detail are finished weights." But a glance at the provided stack-up shows both 1 oz. inners and outers.

Remember, the first fab note specified FINISHED weights. This is not a problem for an internal layer, as they are "print and etch" for the most part. Their desired copper features are protected by the photosensitive resist and are simply printed, developed (to remove the resist not hardened by the light source), etched (to remove the unwanted metal) and resist stripped to remove the resist covering your desired copper features. So a 1 oz. callout for an inner layer is not at all uncommon.

The 1 oz. finish for the outer layers, however, is a bit unusual, given the fact that IPC recommends a minimum of 8/10 of a mil of plated copper on the surface and in the barrel of the hole for continuity. So starting on .5 oz. or even .25 oz. copper foils would mean we would have to plate less than what IPC recommends to finish at 1 oz.

# COOLSPAN® TECA

thermally & electrically conductive adhesive

### Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

Advanced Connectivity Solutions www.rogerscorp.com

#### MEET YOUR COOLSPAN® TECA FILM SUPPORT TEAM

#### Leading the way in...

- Support

- Service

- Knowledge

- Reputation

SCAN THE CODE TO GET OUR CONTACT INFO.

Greg Bull Applications Development Manager Northern & Eastern Territory (U.S.) & Canada

Dale Doyle Applications Development Western Territory (U.S.)

John Dobrick Applications Development Manager Southern

Manager Southern Territory (U.S.) & South America

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan Worse yet, there may be impedance calculations that the customer has based on the 1 oz. finish for outer layers. Increasing the finished copper weight may mean a REDUCTION in your impedance lines. If you have already taken them down to .003" for instance, this may be a problem for the manufacturer.

This clarification about what is needed for desired copper can take additional time at the quote process. I am happy to say we are seeing more and more customers, both old and new, embracing this and creating non-conflicting manufacturing notes that allow for a 1 oz. additional plate.

Now, we see notes that read, "1 oz. inner layers, .5 oz starting copper for outers layers (1.5 oz. finished after plate)." That is a good example of a clear drawing note that does not require

It should also be an obvious point that your notes must reflect the data.

additional clarification or send the fabricator down the wrong road for any external impedance calculations.

It should also be an obvious point that your notes must reflect the data. If you state "IPC netlist compare required," be sure you include the netlist. Likewise, if you have a specific region for placement of a manufacturer logo or date code based on a flag note, make sure that flag note exists.

Remember, a good review of the fab notes for their accuracy and validity prior to release is always a good thing!

#### **9.** Beware of Conversion Errors

Whether it is a conversion error due to format issues or units of measurement rounding, be aware that additional conversion questions can arise at the quote or pre-quote stage.

Example: Lets say your drawing specifies

.0055" traces on layers 3 and 6 to be 50 ohms +/-10%.

This is a nice, round, inch unit measurement. Now, let's say your CAD system is metric and it generates a trace width of .005496. Even this slight mismatch can generate questions that take additional time for clarification. In addition, if you have a number of trace widths that are very close, this rounding error can be misinterpreted easily.

Additionally, simply specifying specific Impedance types by either their name or their net names will not always work. Many manufacturers do not have the ability to query a net name for its location to validate impedances, and the same goes for specifying by their type, such as DDR2, SATA, etc. Not all fabricators are familiar with device names. Which leads me to No. 8...

#### 8. Don't Make Assumptions about Controlled Impedances

When running simulations for the purpose of signal integrity, try to be within +/-10%. Yes, I know this is a tough one.

As a PCB designer, your goal is to simulate impedance to within 10% of your goal. The fabricator should be able to take it the rest of the way. How is this done? Well, typically you will get your marching orders from the engineer who tells you what familiy of materials is necessary for the product. If you simply go online and check material PDFs for the purpose of establishing impedances, be aware of at least two things.

First, look at the dielectric that the dielectric constant is based on. Many material PDFs are based on .014" or even .028" core, so if your impedance lines are .005" or less, you won't be using these dielectrics. The thicker dielectrics also have higher Dk values, which may create an impedance issue.

Let me give you an example: Let's say you have done initial calculation to determine trace widths/spaces based on one of these higher Dk numbers. But in reality, the DK of the dielectric required to meet your impedance with your specified line size is vastly lower, which means an ancrease in trace widths.

If your design is .1 mm (.00393") traces and spaces, the fabricator has NO ROOM to increase

traces to meet impedances, and he therefore has to look at altering dielectric. To add insult to injury, should you have a higher copper weight for the inner layers, it may not be an option to reduce dielectric at all!

Our recommendation is to consult your chosen fabricator prior to trace layout for any tight impedances (traces .004" and less) to ensure they can meet your desired impedance.

Next, consider the speed. If the literature is showing 4.5Dk at 1Mhz and you know this product will be running at higher speeds, such as 5, 10 or even 20 Ghz, understand the Dk will be driving WAY down. You may be looking at something closer to 3.8 Dk at 5Ghz. Again, the mismatch will affect the impedance.

#### 7. Panelization Requirements

If you know where your board will be assembled and they have specific panel requirements for tab placement, tooling hole size and placement, fiducial size and placement, additional panel text or targets you or they may provide a sub-panel drawing to the fabricator. If you do not, and it is acceptable for your chosen fabricator to sub-panelize a given part for you, understand this: While fabricators are generally very good at assosciating breakaway rails with standard .125" tooling holes and .040"-.060" fiducials for auto-insertion devices, should there be a part overhang concern or tab placement concern, it should be communicated to the fabricator at the time of quote. No one likes to redo a panelization after "check plots" have been sent by a fabricator; it takes additional time and additional cost to be "re-CAMmed" to add or modify sub panel features.

So if you do have specific locations where tabs cannot be placed based on feature proximity or edge plate concerns or specific fiducial sizes based on your assemblers preferance, be sure to communicate this with your chosen fabricator at the time of quote.

#### **6.** Specifying Filled Vias

Many of today's products require via fill with either epoxy, silver epoxy, copper epoxy or sometimes even solid plated copper fill.

It used to be that if you needed the vias in the region of a BGA exposed on one side of the board and covered on the other, at 1 mm and .8 mm pitch, the vias could be plugged with soldermask in lieu of epoxy fill without too much issue.

But today with .5 mm and .4 mm pitch devices, the same vias now need to be either epoxy-filled or conductive epoxy-filled depending on whether or not the vias were being used in any thermal management capacity.

Much like with the impedance statement earlier, you may not want to simply specify the location of filled vias by their component names. Make them a unique size. This way you can specify "All .xxx holes to be epoxy-filled and planarized." Or if you are using that same via size where you DO NOT need epoxy fill, create a separate drill file containing only those vioas to be filled. This eliminates guesswork on the side of the fabricator, again speeding things up, minimizing costly revisions and cutting cost.

#### 5. Let's Talk Tolerances

What are typical drill tolerances? For most fabricators here in the US that use inch measurements for tolerances, we typically say +/-.003" for plated holes and slots and +/-.002" for non-plated holes and slots. Are there situations where these would not be applicable but still possible at a fab level?

Yes. Let me give you an example.

Let's say the plated holes in question are to be used for a "press-fit" device and the literature says you need +/-.002", this does not fall into the +/-.003" that is standard, but is still fairly common in the industry and IS possible at the fab level.

Or let's say the holes are vias. As true vias (not part of a plug-in component), they can be specified as +.003" minus the enire hole size. This is particularly useful if space is limited and tells the fabricator you do not care if they are smaller, as long as they provide good continuity.

#### **4.** Avoid Multiple Changes

Whether for a quote or a review, try to avoid multiple changes. If you have decided on a given material family, attempt to stick to a material within that family. If the end-user has not yet decided whether or not a given impedance structure will be co-planar, for example, or even

what thresholds they desire and where they will reside within the stack, soliciting a quote from a fabricator prematurely may make the quote invalid. Consult with your assembler for feedback on any panelization aspects to avoid having to reCAM a panel to add or modify based on assy needs. Lastly, do a thourough product review prior to releasing the fab data to avoid lost time due to incomplete or conflicting notes.

#### **3.** IPC Netlists, Their Function, and Typical Net-Compare errors

What is the purpose of the netlist compare? This method is used to compare your design info against your exported Gerber/image data. This is done prior to any fabrication edits.

Required by Class 3 6012, an IPC netlist contains your design info. You may have heard me say this before, but I have been asked by so many of our customers to CREATE an IPC netlist for a class 3 6012 job if they cannot provide one.

This defeats the purpose of the net compare in the first place. Because the idea is to check the customer's design against the customer's exported data, creating a netlist from that data would never catch an actual design-to-export data mismatch.

What are some things you can check for to minimize time lost for IPC netlist issues?

A. AGND to DGND shorts. You may have an analog ground to digital ground short built into the design. You will want to specify that it is a known or expected short, or you may receive a phone call from your fabricator.

B. Castellated holes (plated half holes at a part edge) practically scream that they will make a connection to a metal grounding post sometime later in life. They come up as "broken" nets frequently when running an IPC netlist compare. They show up as broken only because at the time of bare board fabrication, they dis not make connection to the posts.

C. Surface mounts defined as net points, Likewise, sometimes when a surface mount is defined as a netpoint, we can also come up with erroneous broken or open nets. Again, the netlist may think they are to be connected, but they are only connected after assembly.

#### **2.** Check Your Edges

For scored parts, do not pour metal any closer to the part edge than .015" for an .062" thick part and at least .009" for an .031" thick part.

#### **1.** Get Accurate, Timely Quotes

How do I make sure I get an accurate quote? It's easy. Don't leave anything out. Don't leave anything open for interpretation.

Don't provide a preliminary drawing that you KNOW will change. If the prelim drawing indicates you will have 1,000 vias of a specific size and the final data comes in as 10,000 vias, your price will change.

If you have negotiated impedances and a stack-up over time and the data comes in changed, more time will be involved in revalidating the impedances. Time = money.

If the new board is a revision of an older board and only some constraints have changed, make sure the fabricator knows this so he does not reinvent the wheel for some things they have already covered from a previous rev. This could take additional time and delay the quote.

And of course, if you do everything listed in this article, you should end up with accurate, timely quotes.

As always, I appreciate your time. If you have any comments or feedback I would love to hear from you. **PCBDESIGN**

**Mark Thompson** is in engineering support at Prototron Circuits. To read past columns, or to contact Thompson, <u>click here</u>, or phone 425-823-7000, ext. 239.

# lf you can dream it, we can help you build it.

ondon

Sun, July 8 Your City

刀 🖤 🗱

? ? ?

と回毎回楽

FAST

*IERCONNECT*

IDEAS BROUGHT TO LIFE

We provide all the services needed to take your idea into production:

- Board Design

- Product Development

- Embedded Software

- IOT Solutions

- FPGA Design

- Test Engineering

...and deliver them 40-50% less expensively than other service providers! You can use those savings to build the physical product.

Ready to make your dream a reality?

Click here to get started 🔿

sales@fastinterconnect.com | w

www.fastinterconnect.com

# **Design Strategies for Success—and Profit**

#### by Gary Griffin

FAST INTERCONNECT

In today's economic environment, making money on a project is getting more and more challenging. Those years when businesses like mine were practically printing money are long gone.

#### The Good Ol' Days

If you are under 30 years old, you probably do not have this point of reference; it's been one downturn after another for your entire adult life. But for us older folks, times were really good back then. So, what happened?

You happened, as well as a million others like you, or so it seems. In other words, the market is a little cramped now and much more competitive, which dilutes our profit per project. And if you're old school and have not grown into the here and now, you will always feel the profit pinch.

There was a time when PCB designers could name their price and people would pay it, primarily because their PCB design choices were limited. This is not true anymore. Now, you can't throw a rock without hitting a PCB designer, or at least someone who thinks he knows how to design a board.

This is the competition we all face, and it's the reason it is so difficult to justify our prices. We're competing with every designer sitting in a home office in his shorts, drinking coffee and eating toaster pastries, while undercutting us by as much as 50%. Customers are driven by their own profit goals, and a low-ball quote is attractive when they really don't understand the real cost of using cut-rate resources.

So how do we make more money while saving money for our customers? After all, the only reason to be in business is to make money, and that is a two-way street. Vendor and customer relationships go both ways. We provide a service that has value so they can provide a product that has value.

OEMs use companies like mine because they don't want the overhead of supporting an inhouse design engineering department. That was not the case 15 years ago. Seemed like everyone wanted to capture the engineering in-house. However, when business slowed down, this first thing many OEMs did was push us out the door because they did not know the value of the work we did.

# When Speed is a Priority We're Quick on the Draw Priority

High quality PCBs delivered fast, just another reason we are America's Board Shop

sales@prototron.com | prototron.com

#### **Today: Focus on Project Management**

Fast-forward to 2016. Customers are looking for resources who have both the skills and knowledge to help them get their products developed. What designers have to do is demonstrate the value of our services and capabilities. We don't have to do everything alone; it is good to partner with technologists who have a different skill set than yours, and it's an asset to have a full suite of engineering resources at your disposal. I've found that acknowledging that you may not know the answer to a certain question, but you have access to someone who does, is usually well received and respected. Whether you want to disclose that is your decision, of course.

66 I've found that acknowledging that you may not know the answer to a certain question, but you have access to someone who does, is usually well received and respected. Whether you want to disclose that is your decision, of course.

Customers no longer want to manage their PCB design projects anymore. They would rather throw the project over the wall and have us manage it for them. This is where we show our value, and this is worth a lot more to them than just doing a physical PCB layout.

You can see the look of relief on the customer's face when you demonstrate the willingness to manage their project, along with the skills to do so. Customers will keep coming back and more importantly, they will spread the word about your company. This particular knife also cuts the other way; if you screw up their project, the word will spread even faster.

In order for us to manage a project that has many facets, first we need to understand what the customer wants. Simply put:

- 1. What is the input?

- 2. What is the output?

- 3. What does the customer plan on doing with it?

- 4. What do they plan to use to generate the inputs?

- 5. What do they intend to do with the outputs?

These questions open up the conversation and will organically lead you down the path of what they truly want and this will force you to start asking some questions on your own, like the following:

- 1. Do I know how to do this project?

- 2. Do I know someone who knows how to do this if I don't?

- 3. Do I have time?

- 4. How much time is this going to take?

- 5. How will this impact my current projects?

- 6. If I need to get someone else involved, how much are they going to charge me?

Once all these questions are answered, you will be in a good position to create the estimate and a timeline for your customer's project. An important note: Stick to the timeline.

It goes without saying, but I will mention it anyway, when the project starts to change from the original statement of work, there is always the opportunity to renegotiate costs and pricing. Don't be afraid to do this. It is necessary that the client understand that there is value to your time and services and changes are costly in both.

#### When You Become a Design Customer

Next, I want to discuss the customer's point of view and how you should be addressing the choice of their design bureau. We all may wind up needing to outsource design work from time to time.

Let's face it, choosing the right design engineering company is hard. It is like a blind date. I don't know you and you don't know me. Suspicion and distrust are normal, especially when you will be asked to fork over

**TECHNICA, U.S.A.** Fulfilling Manufacturing Needs Throughout the Electronics Industry

# **Design Challenge:**

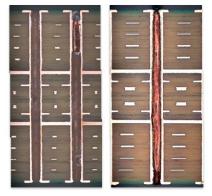

High-speed applications have you asking how low can you go? EMC answers with new very-low and ultra-low loss materials!

#### Introducing EMC's New Line of Copper Clad Laminates

#### EM-891

APPLICATIONS: Very high-speed server, network and telecom PCBs with 25 to 28Gbps per channel design.

#### THERMAL RELIABILITY TEST

- 26L board 130mil

- Pitch Design 0.7, 0.8mm

- Test Condition and Result: IR reflow 260°C 6X <u>with no</u> <u>abnormality</u>

#### EM-891K

**APPLICATIONS:** Ultra high-speed server, network and telecom PCBs with 40 to 50Gbps per channel design.

some of your hard-earned cash to get the project done.

So, one would ask, how in the world do I go about choosing the right company? It really comes down to an interview. Ask the questions that are important to you and to your project, and if you are getting the runaround, then run away as fast as possible.

Ask the questions that are important to you and to your project, and if you are getting the runaround, then run away as fast as possible.

When you are interviewing a potential partner in your project, you need to understand how that company does business. Keep the following questions in mind when you're considering working with a design bureau:

- 1. Do they have and maintain the most current revs of the CAD and CAE software suites?

- 2. Are they willing to spend time with you and outline the process and how it works?

- 3. Do they have the ability to start and finish your project for you?

- a. Do the research.

- b. Create the schematic.

- c. Create the PCB layout.

- d. Completing a prototype assembly.

- e. Developing the firmware.

- f. Perform debug and test.

- g. Provide a technical guide and test report.

- 4. Are they able to integrate your ideas into a final product that you can go and sell to the world?

- 5. Are they willing to protect your ideas and project with a written guarantee and more importantly a legal document?

This process of choosing an engineering partner is a two-way street. The company representative will or at least should be asking you questions and setting expectations on potential costs and potential timelines. They need to understand your ideas, the inputs, the outputs, what you want it to do with them.

Cost is an area of concern. If a company low-balls you on the quote to get your business, caveat emptor, or "let the buyer beware." They ARE going to hit you with additional costs later on, and that is not a good situation at all.

As the customer, you need to understand that if you make changes to the statement of work that was originally agreed upon, cost changes should be expected. After all, their time is worth something too, and this is how they make a living.

Since this may be a long-term relationship, it is important to get to know each other. Talk about the project's goals. Talk about money. Yes, have the money talk. They need to know if you can pay them and HOW you will do so. You need to know what you are going to get for your cash as well as HOW and WHEN.

When they send you the estimate, does it outline the timeline and milestones? It should, and if it doesn't, ask them to provide them for you. If the company cannot give you a timeline and milestones, go somewhere else and start the process all over again.

Finally, a contract is important, because this is your money, your project. You own it, not the design engineering company. Any company should be willing to sign a contract that spells that out.

It's true; the "good ol' days" of electronics design are long gone. But with a little planning, PCB designers can still succeed, and make a good profit too. **PCBDESIGN**

**Gary Griffin** is co-founder of Fast Interconnect, a product engineering company based in Casa Grande, Arizona.

#### BEST-IN-CLASS PRINTED CIRCUIT BOARDS FOR POWER ELECTRONICS

#### **1. SOLUTIONS FOR HIGH CURRENTS**

Heavy Copper Boarde.g. for AC/DC and DC/DC converter

Inlay Boarde.g. for start-stop systems

#### **2. SOLUTIONS FOR HEAT DISSIPATION**

IMS Boarde.g. for LED headlights

#### **Cool Board**

e.g. for cell connectors and battery switches

#### 3. SOLUTIONS FOR HIGH CURRENTS AND LOGIC ON JUST ONE PCB

Power Combi Boarde.g. for electrical pumps

PROJECT HI-LEVEL

#### Smart p<sup>2</sup> Pack<sup>®</sup> (Power Embedding)

- e.g. for electrical motors

- Iow-inductance solutions

- improved electrical, thermal and EMC features

- miniaturisation due to new interconnect approach

Schweizer Electronic AG Einsteinstrasse 10 78713 Schramberg, Germany T +49 7422 512 0 info@schweizer.ag

www.morethanPCBs.com

## The Need for Speed: Strategies for Design Efficiency

#### by Barry Olney

IN-CIRCUIT DESIGN PTY LTD AUSTRALIA

Years of experience with one EDA tool obviously develops efficiency, whether the tool be high-end feature-packed or basic entry-level. And one becomes accustomed to the intricacies of all the good and bad features of their PCB design tool. However, there comes a time, with the fast development pace of technology, that one should really consider a change for the better to incorporate the latest methodologies. This month, I will look at productivity issues that impede the PCB design process.

The choice of PCB design tools, until now, has been limited to either high-end, enterpriselevel solutions that are expensive and have the added cost of an extended learning curve and setup time, or entry-level desktop solutions that are fast to pick up but limited in capability and error-prone. Mentor Graphics' new PADS Professional has addressed this by providing the best of both solutions. Based on proven Xpedition technology, PADS Professional focuses on ease of adoption, ease of use and affordability but is still packed with all the features today's designers need for the most complex designs.

Typically, a high-speed computer-based design takes two or three iterations to develop a working product. However, these days the product life cycle is very short and therefore timeto-market is of the essence. One board iteration can be expensive, depending on your overheads.

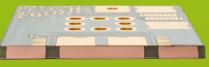

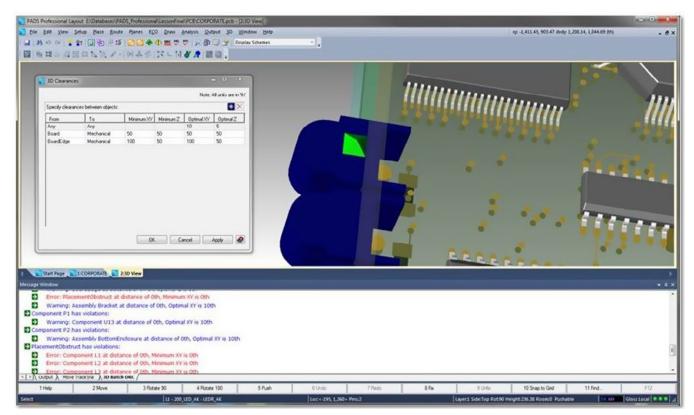

Figure 1: 3D interference validation.

# MECFROM

OPTIMUM TOPOGRAPHY

ULTIMATE ADHESION

#### **EXCEPTIONAL FLEXIBILITY**

#### FlatBOND GT

Ultimate signal integrity meets ultimate board integrity in this treatment for 25 GHz+ designs. Strong bonding with low dielectric resins. *Production proven.*

#### **V-Bond 7710**

Exceptional inner layer adhesion, substantial cost and maintenance advantages compared with oxide alternatives; broad temperature range. *Production proven.*

#### EtchBOND CZ-5480

The industry standard bearer for equipment and process flow compatibility; substantially superior to peroxide sulfuric microetchants.

#### 2030 EtchBOND

The elite adhesion promoter provides highest roughness with least material removal.

Uyemura is committed to providing its customers with significant advantages in performance, cost, and maintenance, and to supporting each program with the industry's finest technical support.

For details on MEC products, or to arrange test processing, contact meonta@uyemura.com, or visit us at IPC APEX, Booth 212.

www.uyemura.com

We should not only consider the engineering time but also the cost of delaying the products market launch. This missed opportunity could cost your company hundreds of thousands of dollars, if not the total loss of market share.

In a previous column, <u>Introduction to</u> <u>Board-Level Simulation and the PCB Design</u> <u>Process</u>, I mentioned that the cost of development is dramatically reduced if simulation is employed during the design cycle. The design changes that occur early in the design process are less expensive compared to those that take place after it is introduced into full-scale production. The cost of the change increases with development time.

Fundamentally, the design changes can be classified into pre-production and post-production modifications. The pre-production changes can happen in the conceptual, design, prototype, or the testing stage. The post-production stage change will happen almost immediately when the product is introduced into production or worse still, be recognized only when the product reaches the market. The later the stage, the more expensive the issue is to fix. The advantage of virtual prototyping is that it identifies issues early in the design process so they can be rectified before they become a major problem.

For years, entry-level tools allowed us to quickly design and build a prototype, some of these based on chip vendor reference designs. Unfortunately, those days are long gone and development teams are finding that they need to employ analysis tools to verify their design before release. One cannot rely on reference designs to actually work in the operating environment. These designs are generally built by R&D teams who have high academic qualifications but little appreciation of design for reliability or manufacturability—the real world.

This in-circuit design, find-and-fix methodology is imperative in today's design environment, where multiple fast rise-time signals propagate at faster and faster speeds with the implementation of each new technology. We no

| ile Edit View Setup Fjiters<br> +   X 🖻 🔞 🕰 + 🖂 +                                                                                                      |                                    | - 🗖 🏘    | 1 - 3- 1. 22       |          |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|--------------------|----------|---------|

|                                                                                                                                                        | ∠ Constraint Class/Net             | # Pins   | Net Class          | Topology |         |

|                                                                                                                                                        |                                    |          |                    | Туре     | Ordered |

|                                                                                                                                                        | ⊞ № (All)                          |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🗄 🦬 DDR2                           |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🕀 汭 DDR2_Unused                    |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🗆 🦮 DDR3                           |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🗄 🦄 Address                        |          | ddr3_address       | MST      |         |

|                                                                                                                                                        | 🗄 🦮 clocks                         |          | ddr3_clocks        | Chained  |         |

|                                                                                                                                                        | 🗄 🦮 control                        | 8        | ddr3_control       | MST      |         |

|                                                                                                                                                        | 🗆 🦮 Data                           |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🖽 🦮 Group0_1                       |          | (Default)          | MST      |         |

| ddr3_group1                                                                                                                                            | E M Group2_3                       |          | (Default)          | MST      |         |

| ddr3_group3                                                                                                                                            | ExpoDemoAnalog3v_(All)             |          | ExpoDemoAnalog3v_( | MST      |         |

|                                                                                                                                                        | ExpoDemoPower0_9_(All)             |          | ExpoDemoPower0_9_( | MST      |         |

| ExpoDemoAnalog3v_(Defa.                                                                                                                                | ExpoDemoPower_(All)                |          | ExpoDemoPower_(Def | MST      |         |

| ExpoDemoPower0_9_0Defa  ExpoDemoPower_(Default)  Gnd  PCL_Diffpairs  PCL_RX_Diffpairs  PCL_TX_Diffpairs  Power  Special  Oearances  Constraint Classes | 🗄 🦮 fs_addr                        |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🗄 🦮 fs_data                        |          | (Default)          | MST      |         |

|                                                                                                                                                        | 🖽 🦮 mictors                        |          | (Default)          | MST      |         |

|                                                                                                                                                        | PCI_Express                        |          | PCI_Diffpairs      | MST      |         |

|                                                                                                                                                        | Power_0_9_(All)                    |          | (Default)          | MST      |         |

|                                                                                                                                                        | Power_1_5_(All)                    |          | ExpoDemoPower_(Def | MST      |         |

|                                                                                                                                                        | Power_1_x_(All)                    |          | (Default)          | MST      |         |

|                                                                                                                                                        | Power_3_0_(All)                    |          | ExpoDemoAnalog3v_( | MST      |         |

| 1 Parts                                                                                                                                                | Power_3_x_(All)                    |          | (Default)          | MST      |         |

|                                                                                                                                                        | Trace & Via Properties / Clearance | s Nets P | arts /             |          |         |

Figure 2: Constraints planning at the schematic level.

# We deliver Advanced PCB Solutions!

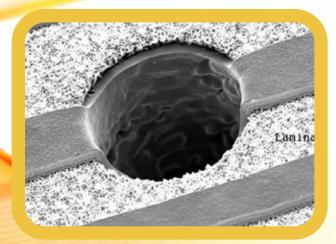

### Landless Via Technology

We're the only manufacturer in the world to have perfected a liquid photo-imageable resist (PiP) in electrolytic form, used for all our production.

CLICK TO LEARN MORE

Our unique processes enable us to create and deliver Advanced PCB Solutions that meet the needs of the demanding market at competitive prices!

### Fine line PCB, 2 mil line /space

We have developed a unique set of processes based on electro-depositable liquid photoresist.

CLICK TO LEARN MORE

#### Impedance Tolerance <5%!

With our panel plating process combined with continuous foil lamination, our impedance tolerances are second to none!

CLICK TO LEARN MORE

CANDOR INDUSTRIES, INC. ADVANCED PCB SOLUTIONS

www.candorind.com | sales@candorind.com | (416) 736-6306

longer have the luxury of building a prototype, testing and then revising the approach where necessary. Virtual prototyping, including signal and power integrity, thermal analysis, DFM and 3D interference validation, impart fewer design spins and are essential for design efficiency. 3D interference validation is shown in Figure 1. 3D clearances can be setup then the 3D clearance checking displays violations and automatically zooms in on the selected violation.

Entry-level tools tend to rely on the skills of the engineer and PCB designer to detect possible issues as they arise during the design process. However, these days a more constraint-driven, correct-by-construction approach is required for complex designs. Once the rules are established, they will be followed by downstream tools and validated to conform by the various design rule checkers (DRCs).

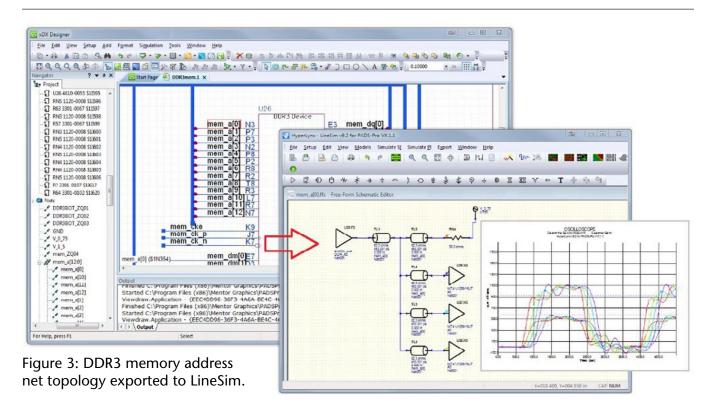

Figure 2 illustrates typical constraints planning and definition for a high-speed DDR2 & 3 design. The constraints should be defined at the schematic level and flow through to the layout process. The advantage of this approach is that the engineer can convey his intent, to the PCB designer, without misinterpretation. Alternatively, the independent engineer (the guy who does everything) can manage the constraints, throughout the design process, using the same consistent management tool. Also, the reuse of constraints from a previous proven design not only ensures consistent rules but also minimizes the possibility of errors.

Net classes are used to organize and speed-up the definition of routing constraints for nets with similar properties. For each net class, the layers allowed for routing, the corresponding trace width range for these layers, and the via types allowed can be defined. For differential pairs, a layer-dependent differential pair gap can be defined based on the calculated impedance to ensure uniform impedance across all layers.

Proper grouping and definition of net classes and constraint classes in the early stages of the design process simplifies constraint definition and management significantly. Grouped constraints can increase layout efficiency, reducing design time and, ultimately, lower PCB design costs.

Pre-layout simulation allows the designer to predict and eliminate signal and power integrity, crosstalk and EMC issues early in the design process. This is the most cost-effective way to design a board with fewer iterations, rather than starting with the post-layout simulation. One

can quickly simulate complex interconnect scenarios including ICs, transmission lines, connectors and passive components to identify which scenario is best suited to a particular design.

An integrated correct-by-construction component library also ensures that once a part is defined, the symbol, cell and part mappings will be in sync. This approach eliminates a major cause of design iterations commonly found in netlist driven design paradigms.

Apart from the use of signal and power integrity analysis tools, most designers still rely on eye-balling to pick up many inconsistencies in the layout. HyperLynx DRC, for instance, can verify complex design rules that are not easily simulated, such as EMC constraints. With support for DRCs of such items as traces crossing split planes, reference plane changes, shielding and via checks, one can quickly detect and rectify issues that may later on causes intermittent signal and power integrity issues. The DRCs can also be customized to allow users to create constraints for any check that they may otherwise perform manually eliminating human error.

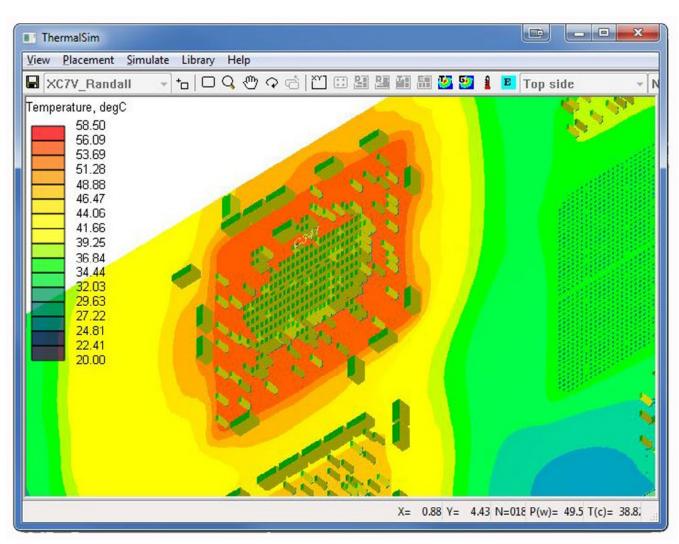

Today's high-performance processors, with sub-nanosecond switching times, use low DC voltages with high transient currents and high clock frequencies in order to minimize the power consumption and hence heat dissipated. However, fast rise times, low output buffer impedance and the simultaneous switching of busses create high transient currents in the power

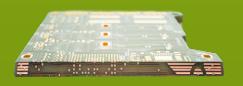

Figure 4: Thermal simulation of hotspots on the bottom of the PCB.

and ground planes. This in turn, degrades the performance and reliability of the product. There is also a high risk of thermal failure in adverse operating environments. Independently from power integrity analysis, thermal analysis can detect hotspots, overheated components and other thermal issues that may degrade the product. Thermal simulation can be run by itself or cosimulated with DC voltage drop. Thermal-only simulation takes into account the heat dissipated from ICs and other components, the environmental air flow and ambient temperature. Thermal/DC drop co-simulation additionally includes the heat produced by current flowing through copper connecting the voltage regulator module (VRM) and DC sink component pin models.

Of course, the use of today's advanced routing technology can provide stunning productivity gains, particularly with the latest highspeed DDR4 memory interfaces requiring your undivided attention to detail. Once set up with constraints defined for all critical signals, routing can be completed and verified in a fraction of the time required using manual techniques.

In conclusion, the use of virtual prototyping including signal and power integrity, thermal analysis, DFM and 3D validation, is now becoming imperative in order to reduce design iterations, meet aggressive schedules and stay ahead of the competition, But, what about the cost? One could choose an enterprise solution that would undoubtedly do the job, or you could consider an affordable bundle of tools that are comparatively priced to desktop solutions, yet provide all the necessary tools required for the most demanding design. Is it time to look at more efficient alternatives?

#### **Points to Remember:**

• The choice of PCB design tools, until now, has been limited to high-end, enterprise-level solutions or entry-level desktop solutions.

• A typical a high-speed computer based design takes two or three iterations to develop a working product, costing engineering time and delaying time-to-market.

• The design changes that occur early in the design process are less expensive when compared to those that take place after it is introduced into full scale production.

• Development teams are finding that they need to employ analysis tools to verify their design before release.

• Virtual prototyping, including signal and power integrity, thermal analysis, DFM and 3D interference validation, impart fewer design spins and are essential for design efficiency.

• Entry-level tools tend to rely on the skills of the engineer and PCB designer to detect possible issues during the design process. A more constraint-driven, correct by construction approach is required for complex designs.

• The reuse of constraints, from a previous proven design, not only ensures consistent rules but also minimizes the possibility of errors.

• Net classes are used to organize and speedup the definition of routing constraints for nets with similar properties.

• Designers still rely on eye-balling to pick up many inconsistencies in the layout. However, DRC tools can verify complex design rules that are not easily simulated, such as EMC constraints.

• Independently from power integrity analysis, thermal analysis can detect hotspots, overheated components and other thermal issues that may degrade the product.

• Today's advanced routing technology can provide stunning productivity gains. **PCBDESIGN**

#### References

1. Barry Olney Beyond Design columns: Introduction to Board Level Simulation and the PCB Design Process, Design for Profit.

2. Steve Hughes, Mentor Graphics PADS Professional documentation, <u>Why Impose Design</u> <u>Constraints?</u>

3. For information about PADS Professional, <u>click here</u>.

**Barry Olney** is managing director of In-Circuit Design Pty Ltd (ICD), Australia. This PCB design service bureau specializes in board-level simulation, and has developed the ICD Stackup Planner and ICD PDN Planner software. To read past

columns, or to contact Olney, <u>click here</u>.

The ANS team is devoted to technological innovation as well as providing our customers with a high rate of satisfaction and speedy service. With our strengths in R&D, we produce PCBs that meet your specific requirements promptly, and at competitive prices.

The ANS mission is to pursue product and service excellence through continuous improvement in a quest for Total Customer Satisfaction.

Head office: ANS Industrial Co. Ltd. Kowloon, Hong Kong Tel: (852) 2757 1882

#### www.anspcb.hk

#### REQUEST A QUOTE TODAY!

#### Factory:

Remapp PCB (Foshan) Co.,Ltd. Guangdong Province, China Tel: (86) 757-8862 3888

#### Email: sales@anspcb.hk

#### **PRODUCTS**

Blind/Buried/Stack via technology

Heavy copper /Pressfit Technology

Multi-layered aluminum board lead-free HAL

8 layer rigid-flex 30mm flexible finished thickness

#### Happy's Essential Skills: The Need for Total Quality Control (Six Sigma and Statistical Tools), Part 2

The statistical representation of Six Sigma describes quantitatively how a process is performing. To achieve Six Sigma, a process must not produce more than 3.4 defects per million opportunities. A Six Sigma defect is defined as anything outside of customer specifications.

#### What a Long, Strange Trip it's Been and It's a Long Way from Being Over

Harvey Miller has been in the PCB industry for more than 40 years, and he's probably seen it all. I recently sat down with Harvey at a wine bar in Palo Alto to learn more about his history in the industry and where he sees it going forward. Harvey arrived wearing jogging shorts and running shoes. No surprise after what his doctor recently shared with him.

#### **Graphic PLC Receives Training Awards**

The awards recognise exceptional training and development in organisations across the South West; celebrating companies that develop their staff through training and have as a result seen exceptional business success.

#### TTM Technologies Reports Sales Growth in Q4 and FY 2015

"Our solid fourth quarter execution combined with seasonal growth in the cellular phone end market and robust demand in the automotive and aerospace and defense end markets drove our sequential increases in gross margin, operating profit and strong free cash flow generation," said Tom Edman, CEO of TTM.

#### <u>Conflict Minerals: Negotiations Begin</u> in Europe on Proposed Legislation

Informal negotiations between the EU Council, Commission and Parliament (trialogue) started on the conflict minerals dossier on February 1, 2016. The trialogue is an informal, closed-door process in which the Council and the Parliament try to reach to a compromise on a legislative proposal.

#### New Year, New Outlook for the Electronics Manufacturing Industry

As an advocate for the electronics manufacturing industry, my job is to educate and encourage policymakers to create a favorable legislative and regulatory environment for advanced manufacturing to grow and succeed. From that perspective, I think we should be proud of the significant progress we made in several areas in 2015.

#### In Memoriam—Dennis (Denny) J. Cantwell

Long-time IPC member, Dennis (Denny) J. Cantwell, 74, passed away on November 12, 2015. Denny was a very active member of the IPC Flexible Circuits Base Materials Committee until his retirement from Printed Circuits Inc. in 2009.

#### Robots, Wearables and Implanted Devices in the Age of Bionic Health

If you are an electronics manufacturer and you ask your business bankers where their market research suggests growth will come from, they will almost certainly identify medical electronics as a key growth area.

#### How North American Fabricators Benefit from Attending HKPCA

Two New Englanders in Shenzhen. It sounds like the title of a play, doesn't it? Headlining the bill is Peter Bigelow of IMI, who explains to me why even small American manufacturers benefit from attending large Chinese shows like the HKPCA. He's joined by fellow New Englander Alex Stepinski of Whelen Engineering, who discusses drill concepts and the transition to zero discharge.

#### <u>Mr. Laminate Tells All: CEM-3 Reinvents</u> <u>Itself (Again)—or, Atari Game Boards</u> <u>on eBay?</u>

CEM-3 was unusual as the reinforcement was a combination of woven fiber-glass fabric and fiber-glass paper. The resin system was a dicy-cured epoxy resin yielding a Tg the same as FR-4 at the time, of 110–120°C range. Because it was all epoxy and all fiberglass, the properties were electrically identical to those of FR-4.

# VERIFY **OPTIMIZE** ANALYZE PREPARE PANELIZE COMMUNICATE DOCUMENT

# **Ensure PCB Manufacturing Success!**

**CAM350**°

Verify and Optimize PCB Designs for Successful Manufacturing.

Create comprehensive documentation to drive PCB fabrication, assembly and inspection.

Verify Design and Manufacturing Rules Any Time During the PCB Design Cycle.

@2016 DownStream Technologies, LLC. All rights reserved. All trademarks and registered trademarks are the property of their respective owners.

At DownStream Technologies we are committed to delivering comprehensive solutions and workflow process improvements for all your PCB design post processing needs.

#### Visit downstreamtech.com or call 800-535-3226

## The Principles of Hybrid Design, Part 1

#### by Tim Haag

INTERCEPT TECHNOLOGY

The butterflies fluttering around in your gut intensify as you walk down that long hallway to the impromptu department meeting. There have been a lot of rumors, but no one seems to know anything.

You wonder, "Will I even have a job 20 minutes from now?" Then you take your seat for the presentation. But fortunately, the news isn't what you had feared, and instead you find out that your company is merging with Acme Industries. And on top of that, Acme has an urgent need for a new design to be completed, and you've been picked for the job.

So, in front of the VP, your boss, and all your co-workers, this particular hot potato gets handed to you. Congratulations. But as you look through the design data, those annoying butterflies return, because the design requirements are something that you've never seen before. And even though you desperately want to raise your hand when the VP asks if anyone has any questions, you decide to hide your confusion instead. But what you desperately want to ask is; "Just what in the heck is a hybrid design anyway?"

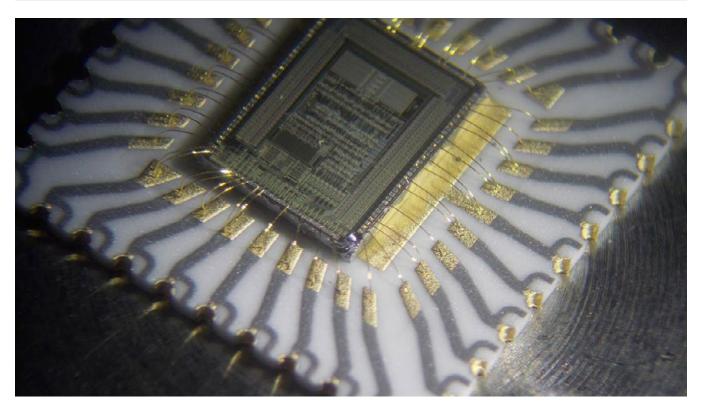

So just what exactly is hybrid design? If the only thing that comes to mind is an image of a car that switches between batteries and gasoline for power, then this column may be just what you are looking for. We are seeing more and more of our customers exploring the world of hybrid design, and we are getting new customers for whom hybrid design is their sole focus. The world of hybrid design is growing and we have lots of hybrid-specific functionality built into our software that helps designers conquer

Figure 1: An example of a hybrid design (Image courtesy of Saline Lectronics).

# When failure is not an option, don't leave your high tech PCBs to Visit us at DesignCon in Booth #1049

# Have an <u>ACE</u> up your sleeve!

- Specializing in high technology quick turn prototypes, as fast as 24 hrs

- MIL-PRF-55110, MIL-PRF-31032A, AS9100, and ITAR certified

- Leading experts in RF, Hybrid

PTFE/FR4 and Antenna/Microwave

#### www.ace-pcb.com

#### sales@ace-pcb.com

the unique hybrid design requirements that they are faced with.

And yet many designers out there (and I used to be one of them) have no idea of what is meant when people start talking about hybrid design. It is therefore not uncommon for designers to avoid the subject directly while hoping to pick up little cues and pointers from others indirectly so that they are no longer in the dark. If that description sounds uncomfortably close to where you are today, then read on. My hope is that this three-part series will help you by serving as an introduction into the world of hybrid design.

And yet many designers out there (and I used to be one of them) have no idea of what is meant when people start talking about hybrid design.

And before we jump in, I want to give a shout out to my colleague Bernd Pflueger. Bernd has been around the world of hybrid design for a long time now, and he has probably forgotten more about it then I'll ever know. I'm indebted to him for his help and the depth of his knowledge and the valuable insight to hybrid design from the PCB designer's perspective that he brings.

A hybrid design is an alternative to the standard PCB. Components and conductors are attached to or fabricated onto a substrate which can then be completely encapsulated in a protective coating. Hybrids are generally smaller and much more robust than PCBs, making them more adept for extreme environmental conditions. A hybrid design is best if the board is going to be subjected to moisture, excessive vibration, or high temperatures. In other words, if a board is going to be immersed in water, buried in the ground, or shaken to death inside the hot confines of some kind of engine, then a hybrid design would be the better choice over a PCB which may not able to survive under those kinds of conditions.

Hybrid designs will generally have a higher reliability than traditional PCBs. They have fewer solder interconnections, while the other metal interconnections in a hybrid design are more reliable than a solder joint. And with the ability to print ink resistors instead of using standard board-mounted packaged resistors, a hybrid design can realize better precision in their resistors plus save on the cost of stocking and storing these parts for manufacturing. But we are getting ahead of ourselves by talking about ink resistors this early in the game; more about that later.

To start with, let's talk about the basic structure of our hybrid design, which for the purposes of this series we will be referring mostly to an LTCC hybrid design (more on what LTCC means later). As the circuit board designer knows, a standard PCB is a made up of different layers of copper and dielectric material (usually FR-4). The PCB fabrication process etches copper away to form conductors (traces and fills) and all layers are eventually composited together. Therefore the fabrication of a PCB can be considered a subtractive process due to the copper etching. An LTCC hybrid design is the complete opposite. It is built bottom-up from a substrate by printing conductive material for conductors (traces and fills) onto the substrate making its fabrication an additive process.

LTCC stands for low-temperature co-fired ceramics. LTCC designs generally use a ceramic material for their substrate, although depending on the needs of the design, different substrate materials can be used. Stainless steel and titanium are two alternatives for substrates, but these materials are more expensive then ceramic and add another level of complexity to the fabrication process. Each of these would require the application of a thin layer of isolation material to the substrate before adding conductive layers. Therefore, the majority of substrates are ceramic unless the high-temperature environments require the extra cost and weight of stainless steel. Titanium is reserved for those environments where heat flow, weight and sta-

# ULTRA HIGH THERMAL PERFORMANCE

Introducing SH-260, a new Polyimide system with Tg > 250°C (TMA)

#### SH-260 IS IDEAL FOR:

- Burn-in boards

- Down Hole

- Aircraft and Aerospace

- Ultra-high count layer boards

- Other PCB high temperature/ long-duration applications

Visit us at IPC APEX Booth 741

CLICK HERE TO LEARN MORE

www.paramount-usa.com

bility under changing temperature conditions demand the additional increase in cost over stainless steel. Stainless steel and titanium substrates are usually used in HTCC designs, and not LTCC.

The word "co-fired" means that the conductors and the ceramic are all heated (fired) in an oven at the same time. LTCC is fired at a temperature of up to approximately 900°C and when in use these LTCC designs can operate in a design temperature range of up to 225°C. This is one of the main advantages over standard PCB designs which are usually restricted to operating temperature ranges that do not exceed 85°C.

We have also mentioned HTCC hybrid designs, and as you might expect, HTCC stands for high-temperature co-fired ceramics. These designs get fired in ovens up to 1500°C and can support operating temperature ranges of up to 500°C. But these designs are also subjected to higher conductor resistance due to the different type of conductive inks required for the higher temperatures. HTCC designs also have other considerations such as the requirement of different methods of soldering components using different mixtures of metals due to the higher temperature environments. Because of these reasons, HTCC technology is used for hybrid designs only if the advantages it provides are truly required.

There are other hybrid technology types besides LTCC and HTCC in use as well. Greentape technology is a blend of both FR-4 and LTCC technologies for high-precision designs. Greentape stacks several thin ceramic substrates, each printed with only one conductor layer, and presses them into a layered package. This technology lends itself to RF and microwave designs for Bluetooth, radar and transceiver applications. But as we said, for the purposes of this series we will focus primarily on the LTCC hybrid design in our efforts to introduce you to the basics of the hybrid design world.

Unfortunately, just as we are getting started, we have reached the end of Part 1 of this series. We've discussed the basic structure of a hybrid design and talked about their benefits, but there's still so much more. I teased ink resistors with a promise of more information, and that is still to come. And we haven't even touched yet on things like software differences for hybrid design applications, routing conductors, or designing dielectric areas, to mention just a few of the topics that still need to be covered.

Therefore, I hope that next month you will look for Part 2 in this series on basic hybrid design, and we will continue down this path of exploration. See you then. **PCBDESIGN**

**Tim Haag** is customer support and training manager for Intercept Technology.

#### Step Towards 'Holy Grail' of Silicon Photonics

A group of researchers from the UK has demonstrated the first practical laser that has been grown directly on a silicon substrate.

It is believed the breakthrough could lead to ultrafast communication between computer chips and electronic systems and therefore transform a wide variety of sectors, from communications and healthcare to energy generation.

The EPSRC-funded UK group, led by Cardiff University and including researchers from UCL and the University of Sheffield, have presented their findings in the journal Nature Photonics.

Silicon is the most widely used material for the fab-

rication of electronic devices and is used to fabricate semiconductors, which are embedded into nearly every device and piece of technology that we use in our everyday lives, from smartphones and computers to satellite communications and GPS.

Professor Peter Smowton, from the School of Physics and Astronomy, said, "Realising electrically-pumped lasers based on Si substrates is a fundamental step towards silicon photonics. The precise outcomes of such a step are impossible to predict in their entirety, but it will clearly transform computing and the digital economy, revolutionise healthcare through patient monitoring, and provide a step-change in energy efficiency."

# Superior Quality Begins Here.

Since we first began in 1985, delivering the highest quality products possible has been our first priority. Our quality control systems are certified and we renew our commitment to quality each and every day.

Delivering quality products on time, combined with timely and accurate communication from our customer service team is how we create lasting relationships with our customers.

## Take a look at our quality »

## **COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

## Design and Production: Some Essential Facts

## by Phil Kinner

ELECTROLUBE

Well, a month has passed since I last appeared in this column offering advice on the importance of design for manufacture, essentially how to spot those wrinkles that might have an adverse effect on production, and iron them out before you even think about applying conformal coatings to your products. I do hope you found it useful and that it has, at least, started the conversation about the importance of making sound early-stage design decisions.

In this column, I'm going to take a look at some issues you are sure to face—which must be taken into consideration—when you finally apply those conformal coatings. Here are my five essential facts:

## Fact 1

Conformal coatings are generally applied in liquid form and are subject to capillary forces and gravity during drying. They are unlikely to yield perfectly straight edges. Often the coating drawing is presented as a rectangular box, and this is likely to cause issues during inspection. Better to specify areas that must be coated and areas that must not be coated. Anything else is a "don't care" area.

## Fact 2

The old adage that "if some is good, more is better" doesn't necessarily hold true with conformal coating. Conformal coatings are designed to be applied at the thickness specified

Figure 1.

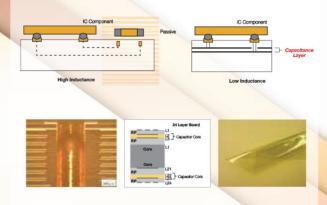

# THE SMART SOLUTION TO IMPROVE SYSTEM PERFORMANCE

## FARADFLEX ULTRA THIN MATERIALS FOR HIGHER PERFORMANCE PCBS

Faradflex is a high performance, ultra-thin laminate or resin coated copper material designed as an integral part of the PCB, module or chip package.

Visit us in booth #924

## FaradFlex<sup>®</sup> Improves System Performance, Price, Quality, and Reliability by:

- Reducing PCB size and/ or thickness

- Utilizing VSP Copper to provide the lowest loss signal for high speed designs

- Increasing functionality

- Improving power distribution (power integrity)

- Reducing the number of SMT Discrete Caps, Traces, Vias, Pads

- Eliminating hundreds (thousands) of SMT and etched and drilled features sites for possible failure on each PCB

For a free sample contact us at: sales@oakmitsui.com or call us at 503-313-1905

EMBEDDED CAPACITANCE

For more information, visit www.faradflex.com

on the datasheet. Exceeding the recommended thickness is unlikely to provide better protection, but may introduce a range of production issues ranging from dramatically increased cycle time to solvent-entrapment, stress-shrinkage/ de-lamination/cracking. If you need a coating on the thick end of the specification, two thin coating applications are better than one thick coating. If you need more thickness than specified, use a coating that is designed to be applied thickly (such as Electrolube's 2K series two-part coatings) or consider a resin product.

## Fact 3

Conformal coatings are not under-fill materials. They generally contain no filler and have relatively Z-axis thermal coefficients of expansion. They have been shown to reduce the lifetime of ball grid array (BGA) and quad flat nolead (QFN) terminations during thermal cycling conditions. If you need to under-fill a device, use one of the many under-fill formulations especially designed for this purpose.

### Fact 4

Conformal coatings are available in many generic types. Each has its strengths and weaknesses. Choose the right coating for the intended use and operational environment, rather than one that is used by your subcontractor or qualified on another product line for a different end-use environment. Be sure to test your design to ensure that it is suitably ruggedized for the intended application.

### Fact 5

Conformal coatings are not generally waterproof. They will allow moisture to permeate, albeit very slowly, through them. This will eventually react with contaminants from production, such as flux, solder and adhesive residues that could ultimately lead to corrosion beneath the coating. Cleaning is therefore highly recommended prior to the application of conformal coating.

I don't pretend that it's an easy task to choose the correct conformal coating for your product, let alone have certainty that you will have achieved the ultimate goal of protecting your electronics by applying it. It's critical to communicate with your conformal coating supplier, whose technologists can help you address your problems and overcome them at the allimportant early design stage.

See you next month. PCBDESIGN