## APRIL 2022 DESIGNOUT MAGAZINE

# Distinctly different.

Our books are written by recognized industry experts. At around 8,000 words, they are unique in that they are able to be incredibly focused on a specific slice of technology.

> "I-007ebooks are like water in the desert ...it's up to you to drink it in order to survive!"

> > Stephen V. Chavez PCEA Chairman, MIT, CID+

## **VISIT OUR LIBRARY**

## LIFE IS BETTER WITH A COMPANION... GUIDE

Put knowledge into action. Download the bonus companion guide to our systems analysis book and get solutions for all your system analysis needs!

### **APRIL 2022 • FEATURE CONTENTS**

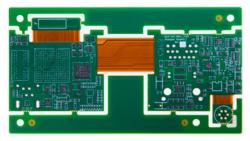

## **Additive Design: The Same, but Different**

As today's shrinking geometries push the limits of traditional fab methods, you need an ace up your sleeve more than ever. Additive processes may be your best bet. This month's issue of *Design007 Magazine* focuses on how readers can get started designing additive and semi-additive PCBs, and how the design process for additive technology differs from that of traditional subtractive processes.

#### FEATURE INTERVIEWS & ARTICLES

12 Additive Design: Same Steps, Different Order Interview with Dave Torp

22 Designing Additive and Semi-Additive PCBs

- by Cherie Litson

- 26 Additive Manufacturing Requires Additive Design Techniques by Luca Gautero

**32 Designing PCBs With Additive Traces** by Tomas Chester

#### FEATURE INTERVIEWS & ARTICLES

60

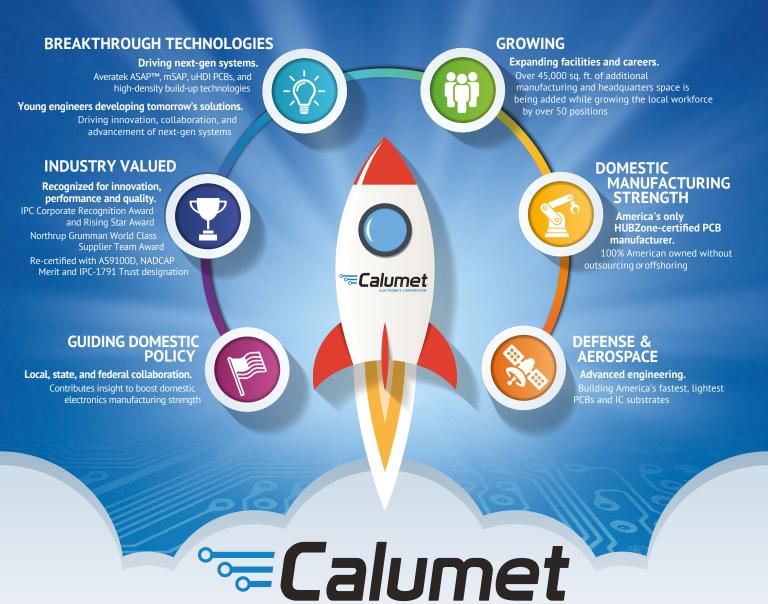

### Calumet on Additive and Semi-Additive Design

Interview with Todd Brassard and Meredith LaBeau

#### FEATURE COLUMNS

36 Burning Questions About Designing for SAP by Tara Dunn

44 Designing for the SAP Fabrication Process

by Barry Olney

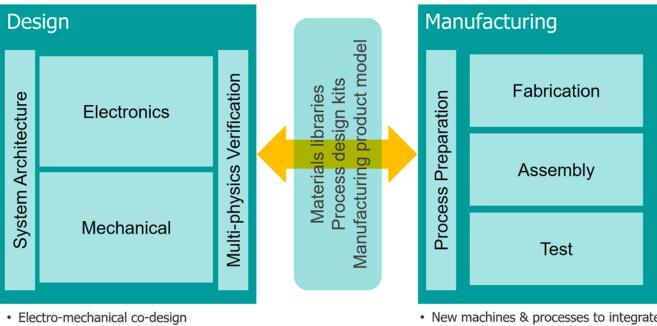

50 The Digital Transformation of Advanced Additive Electronics by David Wiens

4 DESIGNO07 MAGAZINE I APRIL 2022

## ADVANCING GROWTH & INNOVATION

ELECTRONICS CORPORATION

calumetelectronics.com

## **APRIL 2022 • ADDITIONAL CONTENTS**

## DESIGNOOT MAGAZINE

### SHORTS

- 21 It's Only Common Sense: How to Develop Great Leaders

- **30** Trouble in Your Tank: Additive, Semi-Additive and Subtractive Fabrication

- **39** All Systems Go: Find and Fix Thermal PCB Problems Sooner Than Later

- 64 Boeing, AWS Join Forces to Transform Aerospace Design and Manufacturing

- **69** Happy's Tech Talk: Semi-Additive Processes and Heterogeneous Integration

- 88 Helping the World Build Electronics Better

### DEPARTMENTS

**109** Career Opportunities

- 124 Educational Resource Center

- **125** Advertiser Index & Masthead

## HIGHLIGHTS

**70** PCB007

- **106** Top Ten Editor's Picks

- 6 DESIGN007 MAGAZINE I APRIL 2022

### ARTICLES

43 Book Review—The Printed Circuit Designer's Guide to... Stackups: The Design within the Design by Skyler Sopp

**90 DFM 101: Solder Mask and Legend** by Anaya Vardya

### COLUMNS

- 10 Additive Design: The Same, but Different by Andy Shaughnessy

- 40 Leaning into Lean Manufacturing by Matt Stevenson

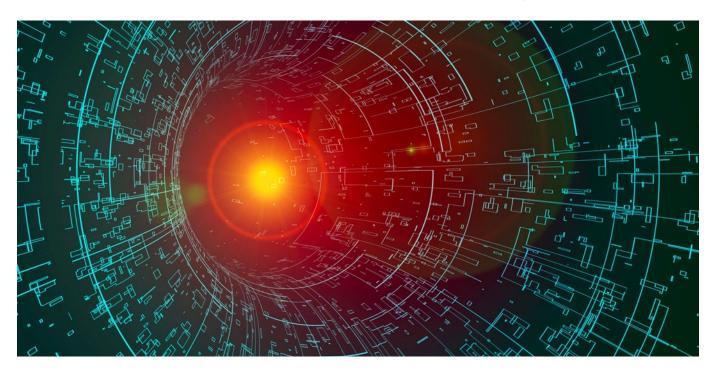

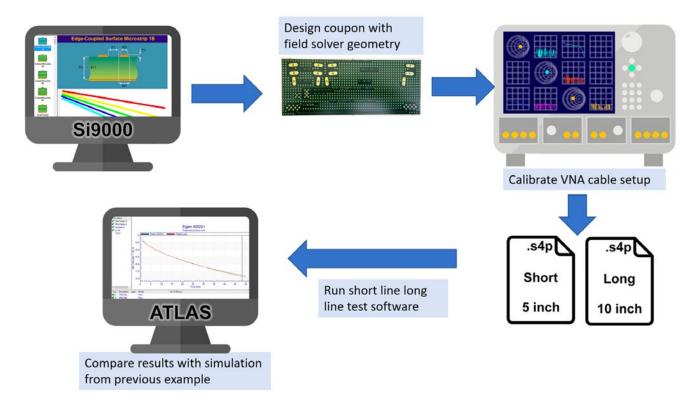

- 54 Using Touchstone Files to Build Measurement Confidence by Martyn Gaudion

- 66 The Importance of Circuit Features for Millimeter-Wave Applications

by John Coonrod

72 Design for Test, Part 3 by Vern Solberg

- **76 Mandatory Masking Guidelines** by Kelly Dack

- 84 Turn Down the Heat, Go Green on Resins by Beth Turner

## autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

### venteclaminates.com

## APRIL 2022 · CONTENTS

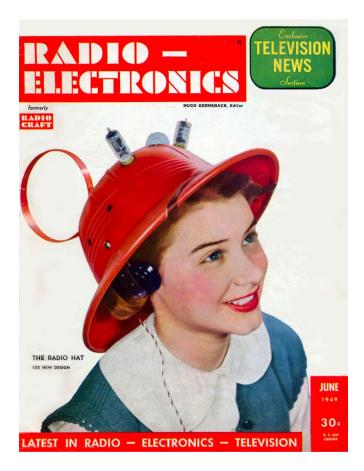

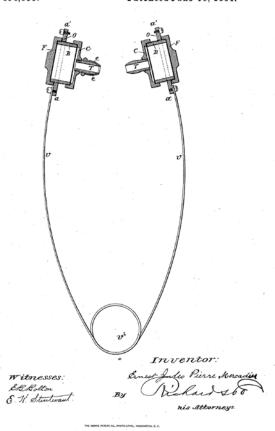

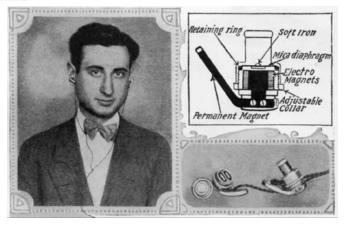

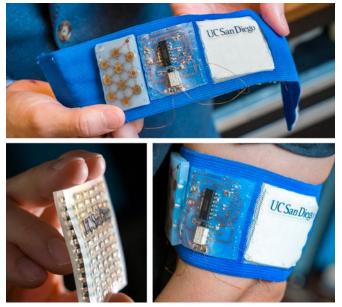

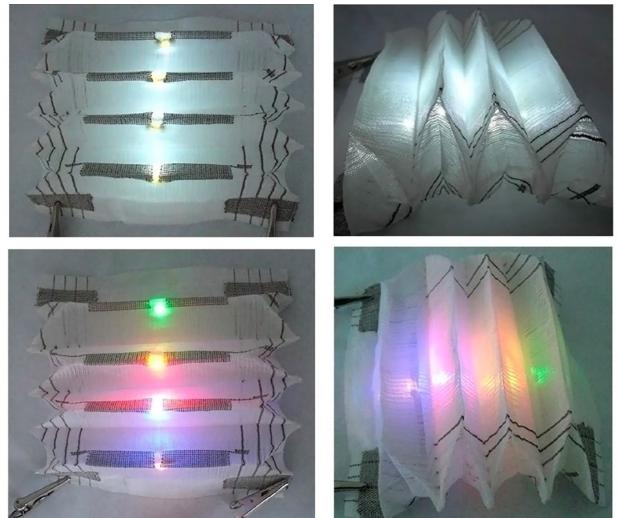

## **This Month in Flex**

Flexible and rigid-flex circuits continue to evolve at a constant pace. Of all of the innovative "twists" on flex circuits, wearable electronics may wind up being the most ubiquitous of all someday. This month, we bring you a column by Joe Fjelstad that delves into the possibilities afforded by wearable electronics.

### FLEX007 COLUMN

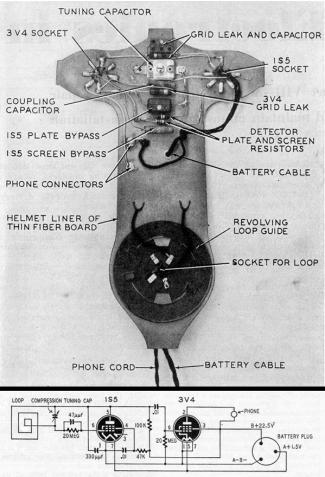

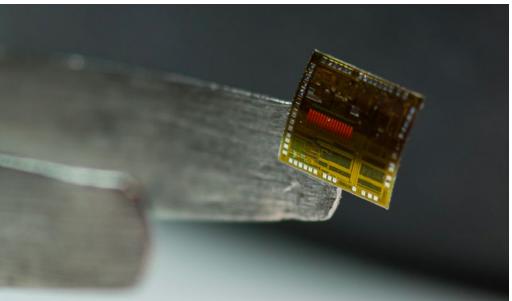

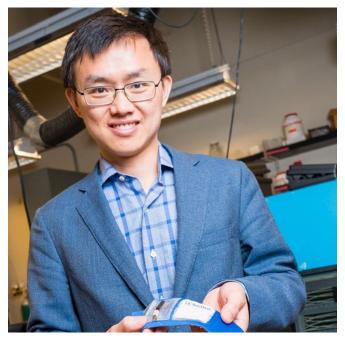

94 The Fascinating History of Wearable Electronics

by Joe Fjelstad

### HIGHLIGHTS

104 Flex007

#### FLEX007 SHORT

**103** Fresh PCB Concepts: The Right Board for the Flex Job

## SUMMIT ACQUIRES EAGLE ELECTRONICS

## READ THE PRESS RELEASE HERE

summit-pcb.com

eagle-elec.com

## Additive Design: The Same, but Different

## **The Shaughnessy Report**

by Andy Shaughnessy, I-CONNECT007

When we decided to focus on designing for additive and semi-additive processes this month, we ran into a challenge much like the one we faced with the February issue of *PCB007 Magazine:* There aren't too many experts on this subject, not to mention educational resources or agreed-upon best practices.

Additive and semi-additive design and manufacturing are in flux, and PCB designers in the additive world are basically making the rules as they go. As instructor Cherie Litson says in her feature article this month, when it comes to additive processes, there are far more questions than answers. Cherie is currently working on an additive design curriculum which she hopes to have ready to go this year. The industry certainly needs more additive design resources.

At recent trade shows, there was plenty of chatter about additive and semi-additive design techniques. Much of it is speculation,

but the interest is there. If your company's high-density boards have pushed traditional subtractive etch fabrication to its practical limits, you're probably already researching additive and semi-additive processes.

Defense and aerospace contractors are very interested in additive. NASA is doing an additive happy dance, and so are consumer device makers who are on the leading edge of miniaturization, in the arena of ultra-HDI. If you need spaces and traces below 1 mil, additive is an attractive option.

It's not that subtractive etch can't go below 1 mil spaces and traces. Traditional fabrication processes can go below 1 mil, but the boards become burdensomely complex, which is going to cost you—in extra routing and via layers, and increased lamination cycles, which drive up cost and drive down reliability and yield.

Additive and semi-additive processes seem to be a better way, at least so far. Additive can produce spaces and traces 0.5 mils wide and smaller, and the laminate itself can be thinner, too. And the additive traces are beautiful, with straight walls—not trapezoidal. For 60 years, fabricators and designers have wondered what it would be like to have perfectly straightwalled traces, and now we can find out.

But there are plenty of potential pitfalls. In fact, we don't even know what we don't know, as Pentagon spokesmen like to say. How does a designer get involved in designing additive PCBs? What resources are available? When does it makes sense to use additive or semiadditive vs. traditional? How are signal integrity, crosstalk, and impedance affected by these new constructions? Where is the sweet spot? Do today's EDA tools support additive and semi-additive?

This month's issue of *Design007 Magazine* will focus on how readers can get started designing additive and semi-additive PCBs, and how the design process for additive technology differs from that of traditional subtractive processes.

In a conversation with Dave Torp, he discusses additive design techniques and why the design cycle is similar to traditional design, but in a different order. Cherie Litson walks us through the steps in additive and semi-additive design, including DFM and signal integrity considerations. Luca Gautero explains how solder mask is applied during additive processes, and how this affects the design rule check guidelines. Columnist Tara Dunn answers some of the many questions designers have about designing boards made with semi-additive (SAP) processes. Tomas Chester addresses designing PCBs with additive traces.

Columnist Barry Olney discusses a typical SAP design process, its benefits and challenges, and why SAP may be part of a natural manufacturing evolution as lines and spaces grow increasingly denser. Dave Wiens explains how today's EDA tools will have to adapt to optimize the design cycle for additive and semi-additive PCBs, and Calumet's Todd Brassard and Meredith LaBeau detail some of the hurdles facing designers who move into additive PCBs, and why a little competition here would help get this technology standardized.

We also have columns from our regular contributors Matt Stevenson, Martyn Gaudion, John Coonrod, Vern Solberg, Kelly Dack, Beth Turner, and Joe Fjelstad. Finally, we have a review of *The Printed Circuit Designer's Guide* to... Stackups: The Design within the Design by Skyler Sopp, and an article by Anaya Vardya.

Additive and semi-additive processes are microcosms of the industry—there's a lot of innovation going on. And we'll keep bringing you the design information you need to know. See you next month! **DESIGN007**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 20 years. He can be reached by clicking here.

Feature Interview by the I-Connect007 Editorial Team

We recently spoke with Dave Torp, CEO of Winonics, about the company's additive and semi-additive processes and what PCB designers need to know if they're considering designing boards with these new technologies. As Dave explains, additive design is not much different from traditional design, but the steps in the design cycle are out of order, and additive designers must communicate with their fabricators because so much of the new processes are still proprietary.

**Andy Shaughnessy:** Dave, give us some background on Winonics and your focus on additive and semi-additive processes.

**Dave Torp:** Additive Circuits Technologies is the parent company, which owns two com-

panies. One is Winonics, a rigid circuit board company. The other is a flexible circuit board company called Bench 2 Bench Technologies. Winonics is ISO-9001, AS9100, and ITAR-registered. We have a 52,000 square-foot facility in Brea, California. Bench 2 Bench has a 25,000 square-foot facility, located about 10 minutes away in Fullerton.

From the holistic view, our focus is in the high-reliability electronics market. We focus on the aerospace, defense, and the medical device electronics. Our competitive anchor is providing great service. We don't really put too many boundaries on what we do. Simply put, we're a technology realization company.

We have process patents for applying circuitry and metallization in an additive technology. We also have some trade secrets that

## Industry Intelligence for the Data-Driven Enterprise

by **NEXAR**

Leverage years of data from across multiple touchpoints in the electronics industry for the most complete and actionable view of the current electronic component landscape.

Avoid disruptions

Eliminate production delays

Gain a competitive edge

$\bigtriangledown$

Improve product performance

| INDUSTRY INDEX<br>83                   | 1    |      | GE<br>3 |    |   |   |   |   |

|----------------------------------------|------|------|---------|----|---|---|---|---|

|                                        | X    |      |         |    |   |   |   | 1 |

|                                        | IDEX | CHAN | IGE     |    | - | _ | > | 4 |

| <ul> <li>Circuit Protection</li> </ul> | 99   | -    | 2       | 1  |   | 7 | 1 | P |

| Connectors                             | 80   |      | 2       | 1. |   | - | - |   |

| Discrete<br>Semiconductors             | 57   | ٠    | Flat    | +  | 1 |   |   | 4 |

| <ul> <li>Electromechanical</li> </ul>  | 82   |      | 4       | -  |   |   |   | - |

| Integrated Circuits                    | 80   |      | Flat    | -0 | - | _ |   | • |

| Optoelctronics                         | 99   |      | 1-0     | _  |   |   |   |   |

| <ul> <li>Passive Components</li> </ul> | 97   |      | 5       |    |   |   |   |   |

| Power Products                         | 92   |      | 3       |    |   |   |   |   |

| Sensors                                | 70   |      |         |    |   |   |   |   |

Subscribe to the Electronic Design to Delivery Index

**Get Free Access**

Visit nexar.com/spectra/eddi to learn more

we keep behind the vest with respect to our manufacturing operations. What the additive technology enables is ultra-fine features and ultra-high definition. The enabling technology provides metallization in very high-density configurations to make high-density interconnects. We have demonstrated the technology down to 15-micron lines and spaces, which was, at the time, the limit of the laser technology that we had.

As the LDI technology becomes more precise, we'll have the ability to go further down that pathway. So, we look to being capable of doing 8-micron lines and spaces and below by 2023.

The real drivers for the technology are miniaturization and the need for greater speed. If you look at some of the frequencies that are required to enable a communication, you are getting up into the 5G-plus mindset. The layer counts within the circuit boards aren't increasing, but the number of interconnects between those layers is increasing. You can have a lot of fun with respect to the layers that are being interconnected and how the microvias are being stacked and racked upon each other. Sometimes you stack them right on top of each other. Other times, you stagger them out a little bit, depending on the signal integrity that you want.

With respect to the additive processes, first we have semi-additive technology, which is a fairly new process. In a lot of cases, you take the ultra-thin copper foils, or the plating applied to the substrate. You hit it with photo-sensitive materials, etch away that ultra-thin part of the copper, and then start to plate back up. That's the semi-additive process.

The fully additive process is the newest technology, where you print the pattern that you want on the substrate without copper foil, using a palladium or platinum-based chemistry, and expose it with a laser or a UV source of radiation. Then you allow the electroless copper plating to be deposited, followed by electrolytic plating

Dave Torp

This allows us to create ultra-fine traces down to sub-15-micron type technology. We're excited about the opportunities, especially in the in-betweens, where you're using hybrid interposer layers to try to connect this heterogeneous integrated package together.

**Barry Matties:** I'm curious about what the challenges are for designers. Are you offering design services, or are you working with designers to help them understand how to efficiently design for additive or semi-additive?

**Torp:** We work with the designers. A lot of the tried-and-true design technologies are based upon the subtractive methodology, whereas the additive methodology is a little bit different. Your sequence of operations and how you build the structures is different. If you want to build a house, are you going to hog it out, or are you going to machine it out of a tree? You've got a big tree and you're going to machine a

house out of it. That's the way the subtractive process works.

With the additive process, you're building from the bottom up, so it's a little bit different methodology as far as how you put the layers together. We work with the designers, and a lot of the military and aerospace guys are looking to get finer and finer features which, within the U.S. footprint, are increasingly difficult to come by. There are very few circuit board shops that can get down to the lines and spaces that we're capable of achieving with the additive process.

**Shaughnessy:** Talk a little bit more about that, Dave. How else is the design process different?

**Torp:** It's different in some respects. You'll find with the ultra-thin foils, if you're familiar with traditional laminate structure, is that it's required to have a tooth on one side, and then you laminate the foil onto the substrate, whether it be the FR-4 or some of the BT or the PTFE-based substrate. You required a little bit of a tooth that acts as a nail, so when you make your copper-clad laminate, you've got to bite into the laminate. With the technology that we're using, it's a chemistry that's applied to the substrate or the prepreg, at that time. It conforms to the contour of the surface, so you wind up with a better bite than you do with these ultra-thin foils, because they just don't have much of a tooth.

If you think of the tooth as a nail that gets driven into the substrate, the adhesion there is minimal at best because you just don't have the length of nail being driven into the substrate. With the capabilities that additive circuits bring, it can conform to every nook and cranny. You wind up with this very, very good adhesion on all layers of the substrates that you're applying it to, and specifically the outside layers of the multilayer, where you need really good adhesion strength. The inner layers are laminated together. You can get away with some minimal adhesion, but on those outer layers, you must have good peel strength, sheer strength, and strength in connection with the substrate.

Then there's the trick of making the microvias between the layers because, typically, you're building the layers up. You're going through plating the vias and the same plating technologies used, but the order of operations to get the via into contact with the capture pad below is a little bit tricky, a little bit different than what people are used to. But we've done the reliability testing. We've sent the assemblies to cap for thermal cycling resistance testing. We're doing very well with respect to the performance of that thermal cycling testing.

As I'm sure you're familiar, that type of testing is meant to shred the microvia into pieces. We were able to survive their -55°C to +205°C thermal cycling without too many issues. We have a few defense electronics-related customers very interested in that technology, particularly on the stuff that's really hard to stick to, which is typically the PTFE-based laminate material. We can get pretty good adhesion onto some substrates that are very difficult to work with. In a nutshell, that's what differentiates us from some of the other processes out there.

**Shaughnessy:** A lot of it sounds like different steps for a designer.

**Torp:** The order of the steps is a little bit different. You're not trying to do it in a subtractive methodology. You're building from the inside out, rather than the outside in. Our website covers a little bit of it, but it's a very proprietary process. Many of our customers are keeping a tight lid on what they do, so it's tough to find information on exactly how to do this. Typically, we work with the designers one-on-one. They have their requirements with respect to impedance and signal-to-noise ratios. They have some ideas of what the end functionality needs to have. Then, we work with them on what's capable. What is stretching it? We invite

the designers to work with us on their specific opportunities and processes.

Then we build prototypes for them, and later they come out and do the thermal cycling and environmental stress testing. They say, "Wow, this is pretty interesting stuff. We didn't quite think about it the way you guys think about it." It's an alternative type of process. Normally, it's in the areas where people struggle with the material set, the low Dk, high-frequency materials set is one that we've had the greatest amount of interest in, especially, from the defense electronics guys.

**Matties:** When you say it's proprietary, is that referring to the design process?

**Torp:** It's the fabrication process. The order of the process is a little bit different than what they're used to, but we're using all the same set of materials that they're used to. From a reliability standpoint, you have similar outcomes; it's just not the same order of operation. You're still using the same electroless copper and electrolytic copper, but the way you're connecting the dots, so to speak, is a little out of sequence.

**Matties:** So, if a traditional PCB designer wants to learn how to do additive design, is it important that they talk to the manufacturer building the board?

**Torp:** Yes, you really need to talk to the fabricators building the boards. That's where the reality, the product realization, comes in. There are not many board fabricators in the world actually doing this, and they're keeping much of their processes under lock and key.

**Matties:** Do you see a growing market for additive and semi-additive?

**Torp:** Yes, there's very big market growth area because the complexity and the number of connections on the board is increasing, especially with the laser-drilling of microvias.

**Matties:** When should the designer consider using additive? What's the trigger point for that decision being made?

Torp: I would say the lines and spaces are the

triggers. Once you start to get below, let's say, one mil or 25-micron lines and spaces, you start to see an increased desire to move toward the additive process, rather than to try to do it in the semi-additive process. It comes down to being able to control plating within the process, and especially your registration at that point. It's a very difficult thing to go below 25-micron lines and spaces.

That's where the designers must tell us what their requirements are, particularly for signal-tonoise ratio impedance. The dielectrics are get-

ting more like glass in terms of trying to get to the operating frequencies where the HF/RF guys operate. This is where additive comes in.

It's just a spooky environment. The highspeed digital stuff is not as bad as the high-frequency designs. I know Happy can expound upon that. The high-frequency engineers are very knowledgeable folks, and they light up when you start to talk about the high-frequency space.

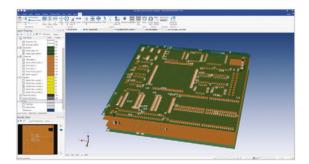

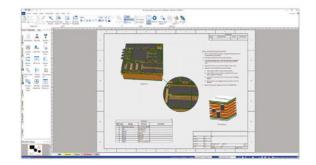

## Support For Flex, Rigid Flex and Embedded Component Designs Now Available.

- Import and Visualize Flex, Rigid-Flex and Embedded Component Designs

- 3D Visualization to Validate PCB Construction and Component Assembly

- Manage Variable Stackup Zones for Rigid-Flex Designs

- Easily Create Custom Flex or Rigid-Flex Fabrication and Assembly Documentation

## For more information visit downstreamtech.com or call (508) 970-0670

**Happy Holden:** You're balancing the losses between the dielectric losses and the copper losses, and the fields that they produce. As things get smaller, with the fields that are active, everything becomes infinitely more complex.

**Torp:** Yes, the high-speed digital is a little bit easier than the high-frequency stuff. I was recently at the IMAPS Device Packaging Conference, and they're really going down in lines and spaces, headed toward glass interposers. They were talking about going down to 2-micron lines and spaces on glass, which is an extremely challenging thing. It's not the revenue center of gravity, at this point. But that's leaning toward the cutting edge, depending on how close you want to be to it.

**Matties:** Now, with the designers working with an additive design, what material selections or considerations should they have in mind? How does that vary?

**Torp:** We're working with a lot of high-frequency materials. We try to stay copper-clad laminate supplier-independent. We like to work with them all. But you start to see more of the higher-temperature, higher-frequency materials—the PTFE and the ceramic-filled type materials. Then, we also do a lot of work on the FR-4 traditional epoxy materials.

Then you start to look at some of the polyimide materials, which have their own set of issues. They move around a little bit. They tend to be a little bit more hydroscopic and create some dimensional issues that you must compensate for. That's the biggest thing with some of the material selections. There are quite a few things happening with additive before we standardize on a process; a lot of the standards are rear-view mirror kinds of things.

**Shaughnessy:** Are there currently IPC standards for additive or semi-additive?

**Torp:** There are some standards and standards committees coming online for additive. There's the Ultra High-Definition Committee that's recently been formed. The Sintering Materials Committee just finished its first publication of a standard, so they're looking at alternative material types with respect to putting metallization down onto the substrates. They're looking at a lot of nano-sintering materials, and copper-based materials to get a copper-to-copper interconnect.

Then there are also committees dedicated to textiles and alternative substrates as well, because people are trying to put this on quite a variety of materials. The IPC does have quite a few new standards committees working on the additive technology; much of it is around the conductive inks that are being supplied to the industry.

**Shaughnessy:** Can you use a regular field solver to model additive and semi-additive designs?

**Torp:** Yes. We've engaged a few designers to help us with signal attenuation. That's not necessarily our core competency. But we do have a couple of folks very good at modeling capabilities who help the designers model the circuitry.

**Shaughnessy:** Very cool. If someone is using any of the main EDA tools, do they have to

do certain workarounds for this, or is it fairly intuitive?

**Torp:** I'd say it's fairly intuitive. The same laws of physics apply, and they just get more accentuated when you start to get into finer lines and spaces. Eventually, you reach a signal integrity barrier that is hard to design around, especially when everything gets tighter and tighter together. You start to look at the edge effects, or the skin effects, that the copper has. You can't have any imperfections in the side walls of the copper, and the surface topography of the copper must be pretty consistent in order to get the signal integrity right, and to be able to model it.

**Shaughnessy:** I know the designers will like the straight walls of the traces. But is there any downside to the straight walls. I'm sure it has an effect on impedance, right?

**Torp:** Yes. Obviously, the conductor has a significant influence on the impedance and the signal integrity. You don't want variations in that conductor width as you move the signal through the conductors. The surface roughness also has some influence over the high-frequency applications.

**Matties:** What advice are you giving designers who are considering additive or moving into additive?

**Torp:** From the design perspective, my words of wisdom are to look at what's realistic in terms of registration. As you go through the lamination process, materials move. Each layer moves in relationship to each other so getting your registration right and making sure that you can

actually align layer to layer to layer, the way you intended it to. It has to do with the signal integrity. Registration, at least with the manufacturing piece of it, is one of the biggest challenges to overcome. Make sure the board fabricator, or the substrate fabricator, can achieve those levels of registration.

**Matties:** You say this market is growing. What year-on-year percentage increase are you seeing in additive?

**Torp:** At this point, the percentage increase is in the double digits CAGR on year-on-year. I think we will reach an inflection point, probably in 2023-24, where it really sets up in significant volume. Right now, very few manufacturers are capable of the types of technology that the industry would like to move forward into as more fabricators and more manufacturing capabilities exist, particularly within the U.S. footprint. You're going to see an inflection point that goes from what is state-of-art to what is a revenue center of gravity. I anticipate that occurring sometime between the end of 2023 and end of 2024.

**Matties:** For designers who are doing high-speed and RF, over the next several years they will probably need learn additive designs, correct?

**Torp:** Yes, I would say within the next two and a half years, they must be a step toward additive and semi-additive processes, and a step away from that fully subtractive technology.

**Matties:** Aside from spacing and finer features, are there any other reasons somebody would go to additive?

**Torp:** There are some interconnect reliability features and functions that start to get involved in the whole design of the assembly itself, of what you're trying to connect. From a design standpoint, especially in the heterogeneous integration piece of it, it all starts with the design because you're now designing a system that will work together. It's not just designing the substrates or the boards. You're trying to marry it up into the shortest distance between the connections. You don't want to necessarily go through long transmission lines between the connections; you're trying to rack and stack things on top of each other.

From a design standpoint, especially in the heterogeneous integration piece of it, it all starts with the design because you're now designing a system that will work together.

You're trying to minimize the losses within the transmission lines that are either in the board or the interposer layers. You want to minimize the number of connections between the dots.

**Matties:** Dave, do you do rigid-flex with additive?

**Torp:** Yes. We look to put additive on polyimide substrates, the backbone of a flexible circuit. While trying to get adhesion to some of the polyimides, we are doing some plasma prep work to rough it up just a little bit, so we get better bite into the polyimides. But we are deploying and employing the additive technology into the polyimides to get that finer line and space. **Holden:** Is the chemical a lot like the E Surface? Is it a nano technology?

**Torp:** The chemical is a palladium base. It's very similar to the old E Surface technology. There have been some twists and turns along the way to get better adhesion, but it's very similar. The patents for E Surface technology are owned by Additive Circuits Technologies and it's similar to what we were doing five to seven years ago. Now, it's just a matter of taking the technology and realizing it in a product, which was missing from the E Surface technology.

With the additive technologies, that Z-dimension starts to become available to you. That wasn't available to designers working with subtractive methods. You can build a construct that follows a certain topography, and that follows a certain geometry or a certain contour around a 3D geometrical design that is different than the traditional laminated flat structure that we're used to. There are some military and defense companies who are interested in putting material into unusual configurations.

**Shaughnessy:** What do you think it's going to take to get additive more into the mainstream?

**Torp:** It's a niche, right now. So, as far as the additive into the mainstream, you need more manufacturers and fabricators capable of deploying the technology and putting it in. It's somewhat like what HDI was in the early days—nobody really wanted to share how they did it. You're all competing for a competitive advantage early on, and then you start to get it into this standardization mode.

The standards committees will be vital in trying to get a set of standards, not only design guidelines, but a set of tolerances for manufacturability of it before it really starts coming into the mainstream. But, if you look at some of the technology that goes into such things as the Apple Watch, and the number of interconnects and sensors inside a relatively complicated device, it's phenomenal the amount of integration they're doing, in a very, very small space. There are not a lot of folks who can deliver that type of technology.

Until that level of technology gets embedded into the mainstream, it will be very difficult. Most of the technology, as Happy knows, is coming out of Asia Pacific, with some coming out of Europe. In the U.S., we're a little behind the curve from a manufacturing standpoint.

**Holden:** It's interesting to see that Nan Ya is going to invest something like \$600 million to

expand for ABF substrate. Are you working with the ABF film?

**Torp:** Yes, we're playing around with it and having some success, but we have more to do before we build a construct completely on the ABF film. It's similar to what we're doing on the polyimide.

Matties: Dave, this has been great. Thank you.

Torp: Thank you all. DESIGN007

## It's Only Common Sense How to Develop Great Leaders

#### by Dan Beaulieu

Editor's note: I-Connect007 columnist Dan Beaulieu focuses his weekly column on helping electronics companies enhance their professional and technical image.

In this column, he takes an inward look at how companies can upskill their employees into leadership positions.

As we know, the biggest challenge facing any business today, no matter the industry, is the lack of good, qualified people. An even bigger challenge than that is finding people to lead those we already have on board.

There are just not enough good leaders today. Notice I did not say managers; I expressly said "leaders" because there is a huge difference. Managers manage people while leaders not only manage people but inspire them as well.

A great leader creates a clear and concise vision of where the company and her team are headed. They spend a lot of time, in fact most of their time, with their team helping them to see the vision and then inspiring them to do their best to achieve that mission. Here's what I see about great leaders.

- Great leaders inspire

- Great leaders create visions

- Great leaders motivate their team to go the extra mile

- · Great leaders show the way step by step

- Great leaders are great teachers and mentors

- Great leaders create a circle or trust with their team

- Great leaders have high values and pass those values on to their team

- Great leaders create passion in their teams

- Great leaders attract the best people

- Great leaders bring out the best in the people they lead

- Great leaders create great leaders

That's the thing I want to talk about today: developing great leaders.

Just as it has become more difficult to find good people, it is that much more difficult to find good leaders. To meet that challenge, companies have been forced to develop their own, to develop them organically. In my opinion, this is the best way to go.

As I have mentioned several times in this column, I have been looking for ways to help companies with their labor challenges. I have been watching webinars and reading books about creating great teams through great leadership by people much smarter than me.

I read at least six books about leadership and then came across a very good book the subject by famous industry guru John Maxwell. His book titled Great Leaders Ask Great Questions: Your Foundation for Successful Leadership, has this excellent section on how to develop leaders.

The following guidelines (in my own words) were inspired by John Maxwell's book.

To read the rest of this column, click here.

## Designing Additive and Semi-Additive PCBs

### Feature Article by Cherie Litson LITSON1 CONSULTING

With components getting smaller and electronic devices becoming more compact, we are reaching the physical limits of the typical etched fabrication processes. To address these limits, new additive and semi-additive processes are being developed to fit into the current fabricators' production lines without too much disruption or extra cost.

That leaves the design engineer with a few questions: Will additive and semi-additive processes really reduce layer count and sizes? Are there signal integrity and impedance advantages and disadvantages? When does it makes sense to switch to additive or semi-additive? Are my DFMs going to be any different?

Answers to these questions and many more are still being developed. However, I've found a few answers that I'm happy to share with you.

First, let's look at liquid metal ink. LMI is ultra-thin and ultra-dense, conforms to any 3D

surface, works with different pure metals and their alloys (copper, gold, silver, palladium, platinum, etc.), and is non-aqueous, which enables low-cost manufacturing.

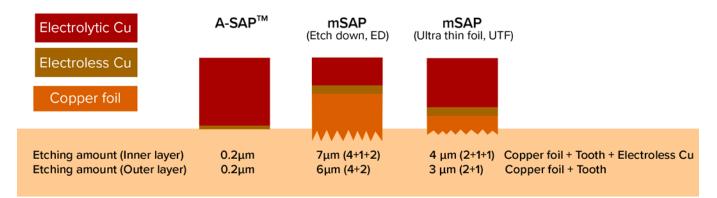

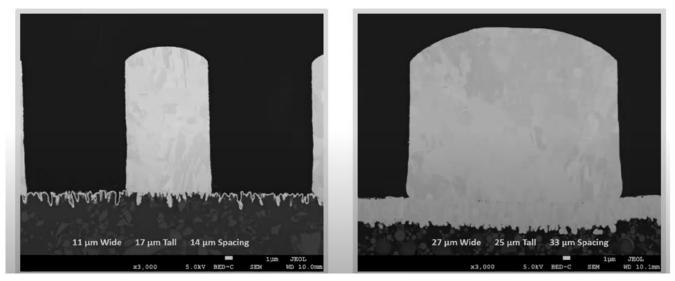

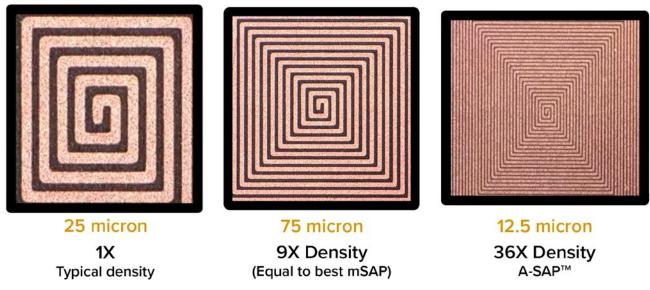

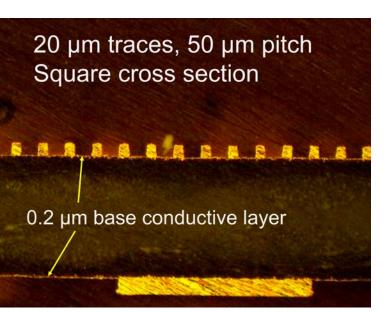

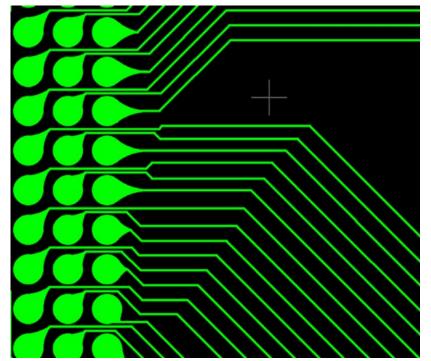

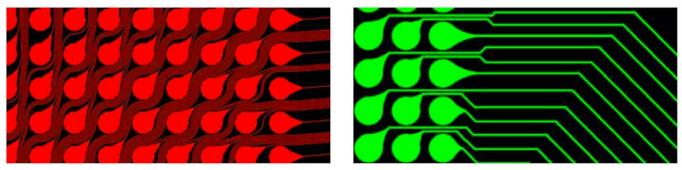

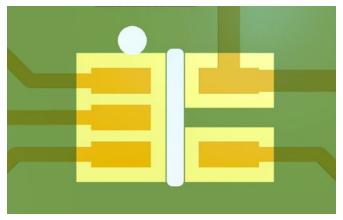

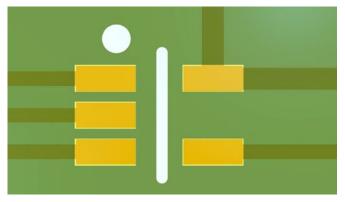

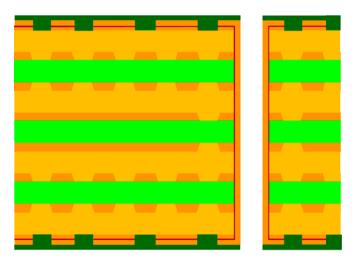

Here are some fundamentals for these very small features. Figure 1 depicts some examples of the additive processes used to create fine copper traces on a printed circuit board. One of the first things you'll notice are the shapes of the traces: They are not trapezoidal. Figure 2 shows close-ups of traces created with additive processes.

Will they really help to reduce layers? Yes, and you still need a good plan for your layer stackup and routing schemes. Everything is just a little different. When the traces get smaller, your dielectric gets thinner. So, it's best to use these either on the outerlayers (foil top designs) or on an inner core pair. They're great for breakout of fine-pitch parts. Just be

Figure 1: A variety of examples of additive processes.

## Smaller is better.

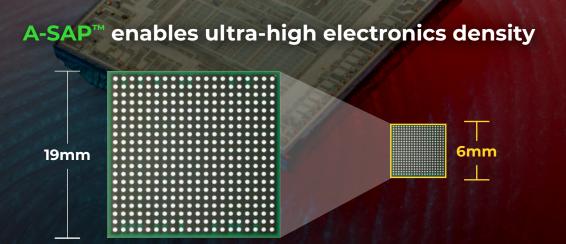

A-SAP<sup>™</sup> Averatek semi-additive process offers a 90% reduction in size and weight over current state-of-the-art with 15 micron (.6 mm) trace and space

A-SAP<sup>™</sup> allows use of much smaller packages

Typical capability in the USA today: 75 microns

A-SAP™: 25 microns and below

More info on A-SAP™

www.averatek.com

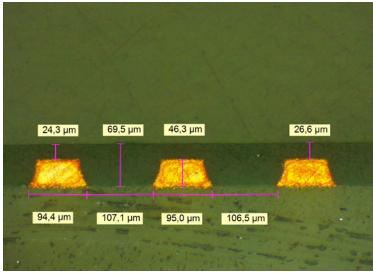

Figure 2: While traditional subtractive traces are trapezoidal, additive traces have straight walls.

sure you leave enough room away from the component pin to allow the solder mask to cover the trace and not your pin. That's usually about a 1.6–2 mil (40-50 micron) space to the trace. Then you can place the traces down to 1 mil apart (25 micron), impedance depending (Figure 3).

Are there signal integrity or impedance advantages and disadvantages with additive? Yes, but it depends on how you look at it. Thinner dielectrics mean thinner boards. This could be positive or negative, depending on your mechanical needs. Current SI calculators don't want to work with a trace width that is smaller than the thickness of the copper.

Speculations are that the high aspect ratio can reduce insertion loss and improve coupling of differential lines, as there is less friction to the material surface. The narrow spacing can improve inductive and capacitive coupling the only thing between the traces is resin, no glass. The process itself allows very precise

Figure 3: Additive and semi-additive processes permit line and space densities up to 36X that of typical subtractive PCBs.

control of the trace/space and can offer tighter control of impedance variations. Now we just need the calculators out there to tackle these new geometries.

When does it makes sense to switch to additive or semi-additive? When you can't get the signal trace density with the current process, or when you can't break out from that 3.5-mm or 3-mm pitch BGA. Don't go there if you only have one component at that pitch. Get a bigger component package instead. For DFM's sake, don't mix small-pitch parts with large power parts on the same side of the board. That will give any assembler nightmares and cost you extra. Also, consider switching when you have very flexible products, need a circuit on a different type of material (like aluminum), if you need to

add copper onto a 3D-printed surface, or create an ultra-smooth conduction surface.

Are my DFMs any different? Yes and no. There are a few things that need to be considered. Normal DFMs still apply. All the typical output files can be generated the same as you would for a subtractive process. You will need

Figure 4: A -section of an additive PCB.

Figure 5: Designing additive and semi-additive PCBs is much like designing traditional PCBs, but with a few important twists.

more notes and direction to your fabricator. You will need to work with a fabricator who has experience with additive or semi-additive processes, and you will need to look deeper at the layer stackup and component placement planning.

I'm compiling a set of DFM guidelines now, and it's not quite done yet. I'll have more information about additive processes in my next article for *Design007 Magazine*.

Get involved with additive design. As miniaturization continues past the practical limits of subtractive etch, additive and semi-additive processes are likely to become more mainstream. **DESIGN007**

All images used in this article courtesy of Averatek.

**Cherie Litson, CID+,** is the founder of Litson1 Consulting and an instructor at EPTAC and Everett Community College. Cherie has more than 30 years of design experience, and has been an instructor since 2003.

## Additive Manufacturing Requires Additive Design Techniques

#### Feature Article by Luca Gautero SUSS MICROTEC

Although I am not a designer by trade, I want to share my thoughts on what additive manufacturing means for designers, especially how it relates to solder mask. The following are the topics I feel are most important to address.

## **1. Definition of Solder Mask**

By its nature, the definition provided by any EDA tool is a negative one; the CAM vector files specify what goes away from an assumed continuous surface. Until now, solder mask has always presented itself as subtractive. SUSS MicroTec developed a front end, JETxSMFE, that can operate at the CAM station to smooth out manufacturing. The software understands

all of this, managing the details correctly on the incoming files.

## 2. The Advantage of Inkjet Solder Mask

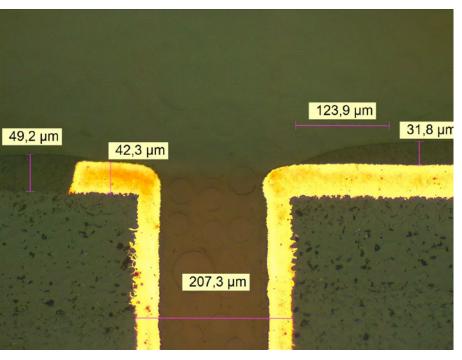

One advantage of inkjet solder mask is to avoid any filling of holes or vias. Another way, maybe an annoyance to some, is to say that "tenting" is not possible. Still, the consensus is that solder mask-free vias improve a board's reliability (Figure 1). The JETxSMFE removes solder mask at declared holes. Undeclared drills, which might still exist depending on the manufacturing convention on the production floor, will result in ink on the print table. This is not a big issue as a scraper easily removes

excess solder mask, and alternatively, replacing the table or its liner (if present) gets the job done. However, both solutions lead to a small downtime. Long story short, if you want friends on the shop floor, be sure to have all the drills in your design.

## 3. The Dam Dogma

These small solder mask traces on laminate are supposed to separate two nearby copper pads. Such a pattern indicates the non-solder mask defined (NSMD) pad design choice. However, this choice involves several constraints, and these create an artificial need for narrow dams. From my earlier example, this time with numbers: Imagine two pads, 200 µm apart, nothing extreme. asc-i.com

## WE BRING MEDICAL ELECTRONICS TO LIFE

With medical electronics, quality, reliability and consistency is critical.

Our commitment to quality and industry-leading technology has served this demanding market for more than 30 years.

How can we serve you?

Check out our capabilites

## American Standard Circuits

Creative Innovations In Flex, Digital & Microwave Circuits

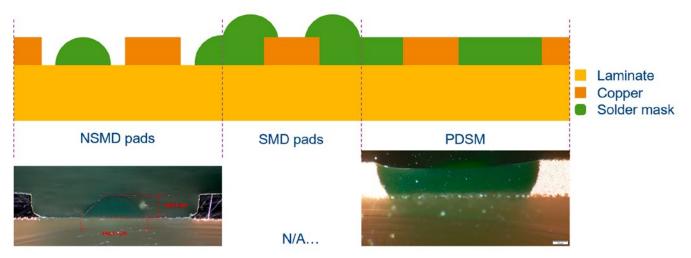

Figure 2: The choices are depicted here as a sketch and as its resulting cross-section.

What is the maximum size of a dam between these two? Assuming that LDI technology is used, the dam size results from applying the state-of-the-art constraint of the technology. This 200  $\mu$ m pitch decreases by the laser beam width plus the registration accuracy twice one for each pad. Therefore, it quickly comes down to 100  $\mu$ m. Any more challenging a pad distance will also make it harder to define a dam.

From this reasoning, the many requests to create 50  $\mu$ m dams or less with traditional technology score logitimate. So what

technology seem legitimate. So, what do we do with inkjet printing? Does it join the race to the last micrometer? No, instead it challenges the initial design choice, which already spurs debate<sup>1</sup>: Will it be solder mask defined (SMD) pad or NSMD pad? Neither of the two. Instead, it will be pad-defined solder mask (PDSM). Unfortunately, this acronym is not a thing yet, so there is no point in googling it. Inkjet is a volumedriven coating technology, which means that filling gaps is possible and, in this case, even encouraged.

## 4. Defining the Thickness

The definition of thickness means that the spectrum between coating conformality (Figure 3) and topographyindependent flatness can be seen (Figure 4). What is the best choice? What solution of thickness design would better fit the solder mask requirements? PCB designers know exactly what the tasks of the solder mask are<sup>2</sup>. Still, the "inkjet upgrade" reviews the basics: While copper without solder mask can oxidize, laminate does not. Copper traces with high voltage without solder mask could create short circuits while bare laminate does not. Therefore, laminate does not need solder mask. The reasons for the solder

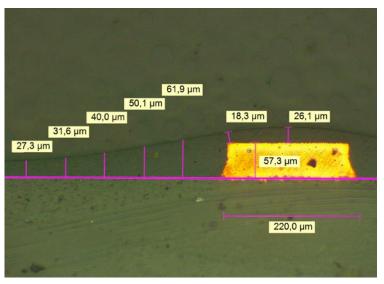

Figure 3: Laminate and copper coating meet the target thickness of 23  $\mu$ m ±5  $\mu$ m. The thickness transition between the two levels is chosen to exceed the target thickness to ensure mechanical stability. (Source: ACB-Atlantec SAS)

Figure 4: An example of a solder mask profile independent of the copper traces. (Source: ACB-Atlantec SAS)

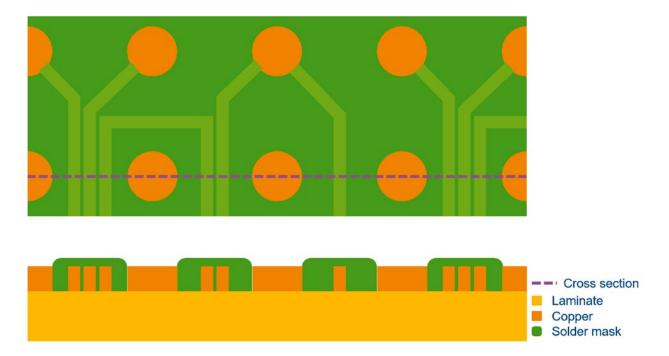

mask coating are convenience (less developer chemistry use) and the need to support any stencil frames. The first is no longer a problem, since inkjet does not use developing chemistry; the second has an elegant design solution: meshes or arrays of shapes to provide the same support with significantly less material coated. When combining the idea of constant coating thickness and the PDSM proposed earlier, a novel level of compactness can open for ball grid array (BGA) structures.

## 5. Design Rule Check

Here is a mélange of considerations which fall under the category of design rule check, where the CAM software will eventually implement them. However, their description here might avoid misunderstandings in the future. The designer will have to know that:

- Solder mask will have a minimum radius. Such radius depends strongly on the inkjet machine chosen.

- The smallest feasible gap between solder mask features is smaller than the smallest feasible printed solder mask feature.

- Thinner solder mask allows for smaller feature size; vice versa, thicker copper or a requirement of thick solder mask will increase the minimum feature size.

Figure 5: What about a more relaxed BGA structure? The traces between pads can have a reduced pitch since inkjet will place a defined volume of solder mask.

- The cross-section of a narrow solder mask feature resembles a dome (Figure 2). The traditional rectangular cross-section is no longer present. Instead, an edge-less, cavity-less profile replaces it that increases mechanical stability and chemical inertness.

- The structuring of the solder mask is based on layers. This means that additional geometrical features on top of the solder mask for mechanical support of components or confinement of dispensed coatings are also possible.

As mentioned, today's CAM solutions cope with the details mentioned above: solder mask thickness, copper thickness and holes. However, it is not yet the right place for defining it. Eventually, it should be something integrated in the CAM software for manufacturing or, even better, already in the designing tool. The final dream is that the components themselves would impose on each location the desired solder mask thickness. This would make it all come together. Designers will put components to rest in peace, this time without a tombstone. **DESIGN007**

#### References

1. "Solder Mask Defined and Non-Solder Mask Defined in PAD," TechForum Digi-Key, November 2018.

2. "What is Soldermask (SM)?" Eurocircuits, 2021.

Luca Gautero is product manager at SUSS MicroTec (Netherlands) B.V. and an I-Connect007 columnist. To read past columns or contact Gautero, click here.

#### **Trouble in Your Tank**

## Additive, Semi-Additive and Subtractive Fabrication

#### Feature Column by Michael Carano

Is seems the operative word today is additive circuit board manufacturing, or for that matter, additive for everything. It is true that the use of additive manufacturing technology has found its way into different industries. While there may be several advantages to adopting additive technology in various industries, one should take a step back and truly assess where we are today in relation to conventional and advanced printed circuit board technology. It makes sense to understand the differences

between fully additive, semi-additive, modified semi-additive (mSAP) and subtractive. In the end, there are several options available to the fabricator and OEM to achieve high density and ultra-density circuitry to support higher end technologies, including IC substrates.

#### Overview

In my opinion, there is much confusion with respect to additive fabrication for printed circuit boards. Well over 45 years ago, there was full build (or "fully additive) circuit technology. One could employ a special pre-catalyzed substrate and build up the circuity with an electroless copper process. However, the circuitry would still need to be formed via subtractive process.

Predating the full build electroless process was the CC4 technology. A microroughened substrate was coated with a metal catalyst, then plated to 25-plus microns over a 24-hour or so period.

> To read this entire column, which appeared in the February 2022 issue of *PCB007 Magazine*, click here.

## Choose wisely.

With today's material performance requirements, it's more important than ever to understand and choose your materials wisely.

## **Designing PCBs With Additive Traces**

Feature Article by Tomas Chester CHESTER ELECTRONIC DESIGN

Advances in technology have been clear to see within the component packaging industry, as the ball grid array (BGA) package sizes reduce from 1.0 mm pitch to 0.8 mm, 0.4 mm, and even beyond. However, while these improvements have occurred with component packages, it has become increasingly more difficult to break out and route the dense circuitry associated with these parts. Currently, the high-density interconnect (HDI) method typically used for the breakout of such parts has been to create the smallest possible subtractive-etched traces with microvias to allow for connections and escapes on the innerlayers of your PCB.

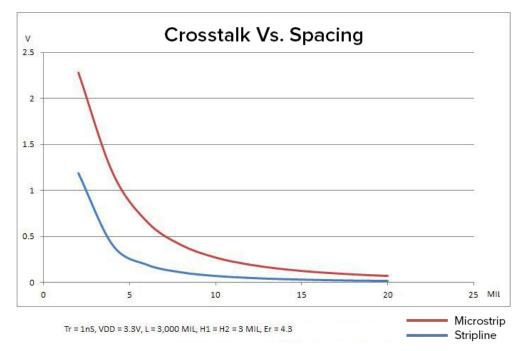

Now there are new fabrication processes that change how we can approach some of these layout difficulties. Additive and semi-additive construction now allows us to get down below 0.075 mm trace and gap sizes easily and reliably, however, utilizing it brings its own series of challenges to the table. Before designers and engineers can start to use this technology, we need to understand the difference between the standard subtractive fabrication method and these new additive fabrication methods, as well as their respective design requirements for trace impedance, and the signal integrity impact from routing traces closer together.

## Manufacture the machine's heart ...

We offer an all-in-one solution through our experience, integrity, and clear communication. Get on board for our joint journey into the future.

www.PCB-technologies.com

PCB TECHNOLOGIES

## Subtractive vs. Additive

Let's start by taking a brief high-level view of the different fabrication processes. With subtractive fabrication, our PCBs start with a base layer of copper of some thickness already laminated to the substrate. Then copper is electrolessly plated onto the board's outer layers, including inside the drill and via holes. A design image is then applied, an etch resist plated onto the exposed traces and holes, after which etching will occur. This is our subtractive step, where we remove the copper in areas where there was no image applied. This is also the limiting step in the subtractive fabrication process, because as we etch vertically down through the copper, the etching agents also remove copper in a horizontal direction, under the applied design image. The result of this process is a final copper trace cross-section with a trapezoidal shape. The critical concern here is that if the trace height is half as tall as its width, likely the etching process will remove the trace.

The critical concern here is that if the trace height is half as tall as its width, likely the etching process will remove the trace.

With additive fabrication, the process can be imagined as similar to 3D printing. The PCB starts with no copper on the laminate material and is instead "built" up on top of a thin seed layer of electroless copper, or on top of a thin laminated copper foil. This not only allows for trace and gap sizes down to 0.010 mm; it also creates a trace cross-section that has a rectangular shape.

Thanks to the manufacturing process, with the formation of these traces now complete, our attention needs to focus on trace imped-

ance. Depending on the impedance calculation, our resultant value is based upon the width of the created trace and the height from the trace to its referenced return path. Whether the construction is stripline vs. microstrip, of course, has some impact here. Typical subtractive-etch processing provides us with an easy and established method for a 0.075 mm trace with 50 ohms of impedance, by utilizing a 0.050 mm thick dielectric material between the trace and its return path plane. This construction becomes significantly more difficult once we move down into sub-0.050 mm traces that you would find using additive fabrication; the dielectric material also needs to decrease in thickness to be able to maintain that 50-ohm impedance, which is where problems exist. Materials that thin, if they are available, are extremely specialized and expensive.

While switching to a coplanar waveguide approach for our trace impedance does offer some minor improvements, our dielectric material thickness still plays a major role in our final impedance.

## **Effects on Signal Integrity**

To complete our overview of additive design, we need to examine its impact on signal integrity. The intended use for these micro traces is to be able to increase our density within our design and assist with dense components. With the decrease in the trace size down to micro traces, we improve our ability to route more traces in a smaller area. However, we understand from our impedance examination that our return path copper remains the same distance away, due to dielectric material thickness limitations. This means that the resultant field size that is created by signals flowing down our traces has stayed the same; however, we have pulled in our neighboring traces closer within that field to increase our design density.

All this comes down to a simple statement: Increasing our routing density also increases the opportunity for crosstalk and other signal integrity issues. To combat possible crosstalk issues, our traces need to be as spread as possible, with return path guard traces where possible. If we need to have traces close together, we want to reduce any parallelism as much as possible by fanning out wherever possible. Finally, we want to group together traces that are a part of the same interface as this will assist with our noise immunity.

Armed with this knowledge, how can a designer or engineer start utilizing this new fabrication method within our designs? One of the first things to do is talk to your fabricator. At present there are a few different additive methods on the market, like A-SAP<sup>™</sup> (Averatek semi-additive process) and mSAP (modified semi-additive process). Each of these has different potential, from trace width to trace heights, so an understanding of your fabricator's capabilities is important to enable design to the appropriate additive specification. The fabricator's capabilities define our minimum trace size, and we already have our crossover point of around a 0.075 mm trace width. Now, it is possible to have additive designs with larger trace sizes, just like it is possible to have subtractive designs with sub-0.075 mm traces; however, that 0.075 mm trace size is a good crossover point to consider switching to using additive design technology.

From experience, designing with additive traces is best suited for those tight or microcomponent package breakouts. It results in a less expensive, more reliable PCB by enabling access to more of the component pins, without needing to increase the number of layers in the PCB. However, the focus needs to be within the package area; once you can route to free space, both trace width and gap should increase. This allows for a small impedance mismatch between the regular trace across much of the PCB, and the small breakout section within the package area.

## **A New Route**

When routing boards that feature additive technology, a designer may experience a slight

mental shift away from the traditional routing method. Typically, once your board's shape, stackup, and constraints have been added into your design, each block or section of the design is then placed and routed on the outer layers of the PCB, with the intent of connecting most of these different routed sections using the internal layers of the PCB. With additive design, coplanar waveguides can be utilized, allowing for increased routing on outer layers of the PCB. This decreases layer count, reduces the number of vias, and maximizes the utilization of every layer.

With additive design, coplanar waveguides can be utilized, allowing for increased routing on outer layers of the PCB.

## Conclusion

Additive and semi-additive processes offer a variety of advantages compared to traditional subtractive etch fabrication. These include spaces and traces as small as 0.010 mm, far smaller than anything possible with subtractive methods, and nice, rectangular-shaped traces instead of the old trapezoidal traces. But with increased density comes the potential for greater crosstalk and other signal integrity issues.

Additive and semi-additive PCBs are likely to become more mainstream. And any designer or design engineer can begin designing additive PCBs—with a little prior planning. **DESIGN007**

**Tomas Chester** is a hardware designer and founder of Chester Electronic Design.

## Burning Questions About Designing for SAP

## **PCB** Talk

Feature Column by Tara Dunn, AVERATEK

Do you have a smartphone? Most of us do. Did you know that most smartphones contain PCBs fabricated with mSAP (modified semi-additive process) technology? The ability for a fabricator to produce 35-micron feature sizes has long been taken advantage of by this consumer market segment. A handful of very high-volume fabricators specialize in this technology and serve the industry. But outside this high-volume market, SAP processes have not been widely available for other lower- to medium-volume PCB applications.

The good news is that this is changing. Fabricators now have access to both A-SAP<sup>™</sup> (Averatek's semi-additive process for PCB fabrication) and mSAP, and the PCB design com-

munity is just starting to scratch the surface to find creative ways for this technology development to benefit next generation electronics. Reduced size, reduced layer count, reduced lamination cycles, and dependence on stacked microvias' increased functionality within the same footprint; the list of benefits can goes on and on.

As the PCB design community embraces the benefits of this newly available printed circuit board fabrication technique, there are, of course, many questions to be answered. This column will address some of the most frequently asked questions related to circuit layer combinations and routing as people are introduced to this new technology.

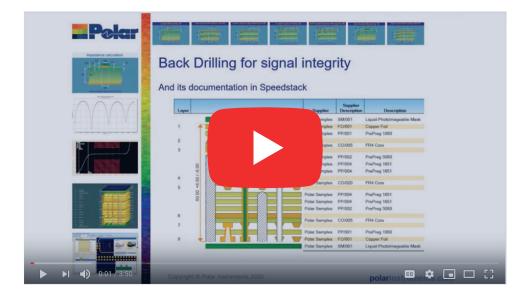

SUBSCRIBE

# Subscribe to the Polarinstruments YouTube channel for helpful impedance and stackup videos

#### PCB Signal integrity tools for design & fabrication

- Impedance & insertion loss modeling with Si9000e

- PCB stackup design & documentation

- Test systems for controlled impedance & insertion loss

- · Application notes on a wide range of Si topics

#### polarinstruments.com

#### What about power and ground layers? Do all layers need to be produced with these ultra-high density feature sizes?

It is most common to use a hybrid approach utilizing both subtractive etch layers and SAP layers in the same printed circuit board stackup. Stackups do not need to be all semi-additive or all subtractive. The layers do not need to be either one technology or the other. Typically, signal layers will utilize SAP technology, often to simplify the breakout of ever smaller BGA packages, reducing the number of layers and the number of lamination cycles required for the design. Traditional subtractive etch technology can then be used for layers that contain only larger feature sizes.

It is most common to use a hybrid approach utilizing both subtractive etch layers and SAP layers in the same printed circuit board stackup.

#### Can SAP processes also produce larger feature sizes? Does the entire layer need to have the same trace and space dimension?

SAP processes can produce larger feature sizes as well. In fact, there are signal integrity benefits to these semi-additive processes that make this fabrication technique sought after, independent of the ultra-high density routing benefits.

Just a quick peek into the fabrication process: The SAP processes move the limiting factor for fabrication from the etching process to the photolithography process. Independent of the seed layer of copper selected, which may be a thin copper foil (mSAP), or an ultra-thin layer of electroless copper (SAP), the dry film resist is patterned, and electrolytic copper is then used to form the printed circuit board traces that were patterned.

The lower limits of those trace capabilities and the tolerance of the circuit traces formed vary based on the process used. The mSAP processes, even with an ultra-thin copper foil, have a seed copper layer that is considerably thicker than the electroless copper seed layer used in the A-SAP process. Because the seed layer of copper needs to be etched where it is not required, the thicker copper will take longer to etch, which impacts the trace itself. Both the line width and space need to be larger with the mSAP process and the line width tolerance will need to be greater than with the A-SAP process. While both processes provide an improved line width tolerance, the A-SAP process with thinner electroless leaves the circuit sidewalls straight with no trapezoidal effect.

Tip: Adjust your modeling software to show traces with no trapezoidal effect and investigate how this changes the numbers. In fact, this should be a topic for a future column.

### Can outer layers and plated through-holes be created with SAP processes?

Yes, a PCB designer can confidently design a printed circuit board with ultra-HDI features on outer layers and connect with reliable plated through-holes using the A-SAP process. When working with mSAP, circuitry on the outer layers is most often discouraged.

Fabricators building with A-SAP have been running regular lots of material using standard D-coupons with stacked and staggered microvias to help PCB designers and OEMs feel comfortable with the reliability of the plated through-holes created with the electroless seed layer of copper I've explained.

## What is the minimum spacing from trace to pad (external layer)?

The copper-to-copper spacing can be a cost adder in subtractive etch processes. In the

semi-additive environment, this is not the case. There are a couple things to consider. First, on innerlayers, this spacing could be 25 microns or below, depending on the technology being used by the PCB fabricator.

Outerlayers need to take solder mask into consideration. There needs to be enough space to allow the solder mask to fully cover the trace and not expose any copper. The thickness of copper typically determines how far you need to be away from the pad. A good rule of thumb would be to use a 50-micron gap.

## What do I need to know to meet a 50-ohm impedance?

First, this topic will be addressed in a future column in much more detail. But I will tease a few high-level tips here. First, be sure that the modeling tool you are using is set for straight sidewalls if you are working with a fabricator offering A-SAP. This does have an impact. Second, pay close attention to copper height. Narrow traces will have higher loss, which is a fact, but decreasing dielectric thickness and increasing copper height do mitigate that. The ability to fabricate high aspect ratio traces (taller than wide) is dependent on the SAP technology used, so be sure to work with your fabricator as your PCB design develops.

There is a lot of work being done to help educate PCB designers about this new technology. This is our opportunity to design with manufacturing and to creatively approach these new capabilities both from a fabrication perspective and a design perspective. We will continue to dive into this in future columns, but please contact me with any burning questions. **DESIGN007**

Tara Dunn is the vice president of marketing and business development for Averatek. To read past columns or contact Dunn, click here.

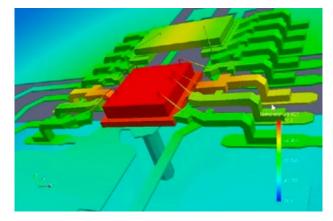

#### All Systems Go! Find and Fix Thermal PCB Problems Sooner Than Later

by Melika Roshandell CADENCE

In an earlier column, "Bridging the Gap Between Design and Analysis with In-Design Analysis," Brad Griffin discussed how the "shift left" that's happening with electronic design means it is no longer sufficient for signal integrity (SI) and power integrity (PI) analysis to be performed in isolation. Designing, analyzing, and verifying the design in its entirety is key. Another facet of this shift left is the need to address thermal integrity (TI) sooner rather than later. In other words, finding and fixing thermal PCB design issues early in the design process is necessary to save costs, reduce design spins, and maintain your own sanity.

Electrothermal co-simulation—understanding the implications (intended or otherwise) of thermal interactions on electrical performance for high-speed (or high-frequency) PCB designs—is now essential for successful end-product development.

Let's start by looking at things from the highest level, which is that we want to design a PCB. At some stage, this PCB (possibly accompanied by one or more additional PCBs) will be mounted in an enclosure. Eventually, this system will be deployed into the field. The designers of the PCB(s) and the system as a whole want to know how well the system will perform and how long it will survive.

To read the entire column, click here.

# Leaning into Lean Manufacturing

#### **Connect the Dots**

by Matt Stevenson, SUNSTONE CIRCUITS

The worst part of the global COVID pandemic brought unpredictability and uncertainty to an otherwise stable PCB Industry. Like many in the board business, Sunstone faced increasing demand from essential businesses while also dealing with inconsistent employee availability and social distancing guidelines that slowed the manufacturing process. We knew immediately that even though the status quo had worked to this point, the situation was not temporary, and the operation would have to adapt.

#### **Commitment to Lean Sustains Quality**

We have been vocal proponents of the Lean manufacturing philosophy for some time, as it is a foundation for delivering quality to our customers. For the past few years, our Lean culture and adherence to Lean principles helped

Sunstone survive and excel during the most challenging business environment in recent memory. COVID renewed and expanded our commitment to Lean principles to sustain the quality of our work and maintain the safety of our employees.

Lean manufacturing is a set of guiding principles aimed at improving efficiencies and productivity—reducing waste in the process. As defined by the Lean Enterprise Institute, the five core principles of Lean are:

- 1. Defining value

- 2. Mapping the value stream

- 3. Creating flow

- 4. Using a pull system

- 5. Pursuing perfection

Lean builds more value into the PCB manufacturing process. Customers benefit from improved products and employees find themselves working in safer conditions. Our Lean work environment made it easier for us to adapt to changing safety requirements brought about by COVID. While many shops struggled with adapting manufacturing processes to social distancing guidelines, Lean practices helped Sunstone more quickly construct a safe, more productive workplace.

The core of Lean is the practice of identifying the true value of every component in the manufacturing process. The pandemic caused us to look more closely at the nature of each task, eliminating those elements of production that did not add value, but perhaps did present

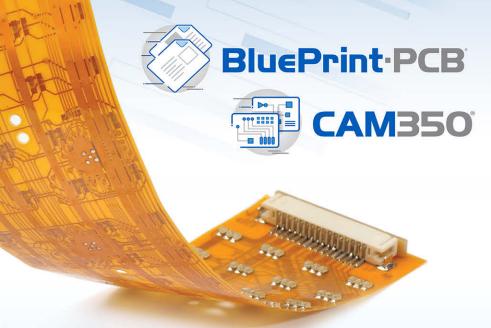

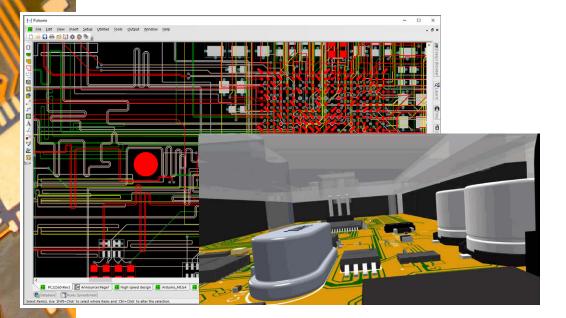

## Integrated Tools to Process PCB Designs into Physical PCBs

Use manufacturing data to generate a 3D facsimile of the finished product.

nsure that manufacturing data is accurate for PCB construciton.

Verify and Optimize PCB Designs for Successful Manufacturing BluePrint-PCB Create Comprehensive Documentation to

Create Comprehensive Documentation to Drive Fabrication, Assembly & Inspection

DownStream Technologies, offers an integrated manufacturing data preparation solution for PCB post processing including manufacturing data visualization, stack-up definition, PCB panel visualization and support for 3D PCB documentation. This environment allows PCB designers and engineers to visualize, verify and document a printed circuit board before manufacturing.

800-535-3226 downstreamtech.com ©2019 DownStream Technologies, Inc. All rights reserved.

risk of transmission. This enhanced attempt to eliminate waste helped us become more profitable, improved employee productivity, and removed unease about COVID risk in the workplace.

#### Adherence to Lean Practices Makes the Difference

At the outset of the pandemic, we didn't really have a grand plan to reinvigorate all five Lean manufacturing principles. We just knew we had to adapt to the drastically changed operating environment. Focused on customer satisfaction and employee safety, we took what we were already doing and amplified it to meet each new challenge COVID brought with it.

There was no formal decree about using Lean philosophy to respond, but with the benefit of hindsight, it was clear that was exactly what we did. Like muscle memory that results from persistent training, we relied on our experience with Lean throughout. Even if our efforts to deal with COVID didn't always result in a classic Lean project or structured application of its principles, Sunstone's adherence to Lean manufacturing got us through the hardest times and put us on a path to come out stronger than when we went in. Now, two years after the initial shutdown, we have maintained operations, kept all our employees healthy and employed, continued to satisfy our customer needs, and reacted quickly to environmental changes.

#### **Dedicated Leadership Lights the Way**

None of that would have happened without dedicated leadership across the organizational chart. Success with Lean has always required executive management commitment to the core principles. When COVID hit, that commitment was front and center, and communicated throughout the organization. We set expectations appropriately at every level, and recognized small, early victories to build momentum that would take us through the worst of the pandemic.

That momentum was sustained by clear, two-way communication throughout the organization. The great ideas for process improvement and safety enhancement come from the personnel doing the work each day. By keeping the channels of communication wide open, company leadership was ready to hear about opportunities to effect change.

Even with normalcy closer on the horizon, the competitive landscape of the PCB industry may be permanent. If last year taught us nothing, it was that economic disruption can come from anywhere. We can't predict what the next challenge will be, but we can be as prepared as possible before it arises. Lean offers a path to readiness, one that considers value for the customer and safety for the employee. By making Lean decisions on everything from equipment type to production floor layout in the midst of a crisis, we found ways to improve process we had never even considered in the past. **DESIGN007**

Matt Stevenson is the VP of sales and marketing at Sunstone Circuits. To read past columns or contact Stevenson, click here.

## The Printed Circuit Designer's Guide to... Stackups: The Design within the Design

#### **Book Review by Skyler Sopp**

If you have ever contemplated crosstalk, eye closure, power loss, or a list of other issues defined in this textbook, then you also need to understand what, why, and how stackups can and will impact your circuit's performance. After all, the stackup is one of the few things that directly touches every single part of your design; therefore, you must set yourself up for the highest probability of success by establishing a strong foundation through a well-designed stackup.

There are many incredible resources out there for those in the high-speed design industry: Eric Bogatin's *Signal & Power Integrity Simplified*, Lee Ritchey's *Right the First Time*, and a host of other books and websites. However, there is an apparent void in the realm of stackup design. How has industry gone so long avoiding such an important topic as one that influences everything on the board? *The Printed Circuit Designer's Guide to... Stackups: The Design within the Design* begins to fill the industry-wide void in an easy-to-understand overview that helps define the aspects that you as the engineer need to be thinking about when putting together a stackup.

With 25 years of experience in PCB manufacturing and signal integrity, author Bill Hargin is an expert in the field of stackup design and it shows here. In Chapter 3, Bill shows how your dielectric of choice will directly impact your "eye." He explains the breakdown of how each variable contributes to the overall loss budget, then defines how he recommends material planning before any routing has begun. This book helps the reader establish the variables of interest and the impact of those variables, and makes a recommendation on what to do about it so you can improve your future designs.

Boards are getting thinner, power requirements are increasing, and routing densities are becoming finer. You will need to make compromises in your stackup, so understanding that trade space is vital. This book breaks down concepts like board loss, material selection, impedance planning, and more to help you understand how each one of them will influence your design when fabricated. This book will assist you in learning how to make educated compromises earlier in the design cycle.

If you are a hardware or electrical engineer who is not already deeply invested in stackup design, this book is really for you. It is full of practical information, not bogged down by technical jargon, has easy to understand and useful images, and gets you off to the races quickly. Even the seasoned veteran will find this book a worthy reference for understanding when one needs to know things like the contribution percentage of each variable on impedance. Regardless of where you are in your stackup knowledge, I recommend downloading the book and reading it! It will be well worth your time and may just save you future headaches. **DESIGN007**

**Skyler Sopp** is a signal integrity engineer for Mercury Systems.

# Designing for the SAP Fabrication Process

#### **Beyond Design**

Feature Column by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

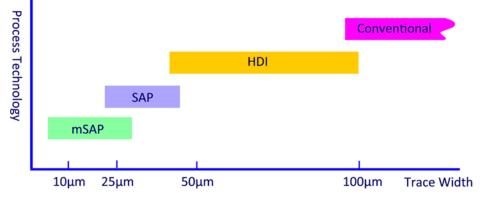

PCB designers are continually challenged with demands for reduced product size. However, form factor-driven design pressures have been relieved, in part, by the increased use of high-density interconnects (HDIs), which enable more functionality per unit area than conventional PCBs. Leveraging finer lines, thinner materials, and laser-drilled vias, HDIs have played a crucial role in device miniaturization. However, the traditional PCB subtractive etch processing becomes very difficult for feature sizes below 3-mil trace/space. This forces PCB designs to become more complex as electronics packages shrink-adding extra routing layers and microvia layers, and increasing the number of lamination cycles required, which impact yield, reliability, and thus cost.

As smartphone technology evolves to 5 Gbps, the PCB industry's approach to HDI manufacturing has also evolved. Vast multiple input/output antenna configurations and increasingly complex RF front-ends expand

Figure 1: Trace width vs. process technology.

the RF content footprint. The higher bandwidth inherent to 5G requires much stricter impedance control. If not formed with extreme precision, the thinner traces of HDIs can introduce an increased risk of signal degradation. To fulfill these demands, the amount of available space for HDI PCBs, within 5G smartphones, needs to be significantly reduced.